# 100 Pin Enhanced Super I/O Controller with LPC Interface

## **FEATURES**

- 3.3 Volt Operation, 5 Volt Tolerant

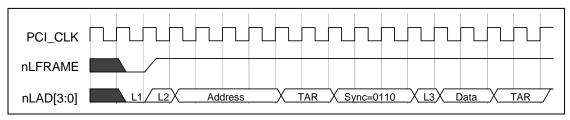

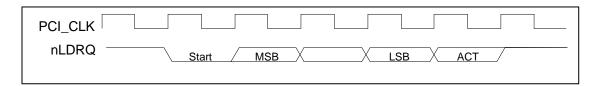

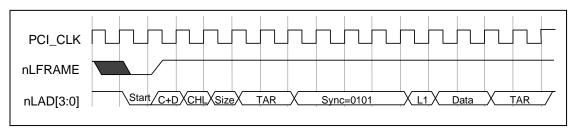

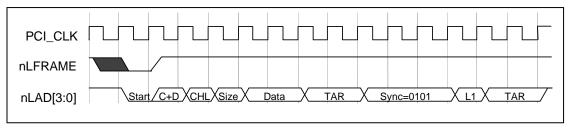

- LPC Interface

- Fan Control

- Fan Speed Control Outputs (2)

- Fan Tachometer Inputs (2)

- Programmable Wake-up Event Interface

- PC98, PC99, and ACPI 1.0 Compliant

- Dual Game Port Interface

- MPU-401 MIDI Support

- General Purpose Input/Output Pins (37)

- ISA IRQ to Serial IRQ Conversion

- ISA Plug-and-Play Compatible Register Set

- Intelligent Auto Power Management

- System Management Interrupt

- 2.88MB Super I/O Floppy Disk Controller

- Licensed CMOS 765B Floppy Disk Controller

- Software and Register Compatible with SMSC's Proprietary 82077AA Compatible Core

- Supports Two Floppy Drives Directly

- Configurable Open Drain/Push-Pull Output Drivers

- Supports Vertical Recording Format

- 16-Byte Data FIFO

- 100% IBM® Compatibility

- Detects All Overrun and Underrun Conditions

- Sophisticated Power Control Circuitry (PCC) Including Multiple Powerdown Modes for Reduced Power Consumption

- DMA Enable Logic

- Data Rate and Drive Control Registers

- 480 Address, Up to 15 IRQ and Three DMA Options

- Floppy Disk Available on Parallel Port Pins

- Enhanced Digital Data Separator

- 2 Mbps, 1 Mbps, 500 Kbps, 300 Kbps, 250 Kbps Data Rates

- Programmable Precompensation Modes

- Keyboard Controller

- 8042 Software Compatible

- 8 Bit Microcomputer

- 2k Bytes of Program ROM

- 256 Bytes of Data RAM

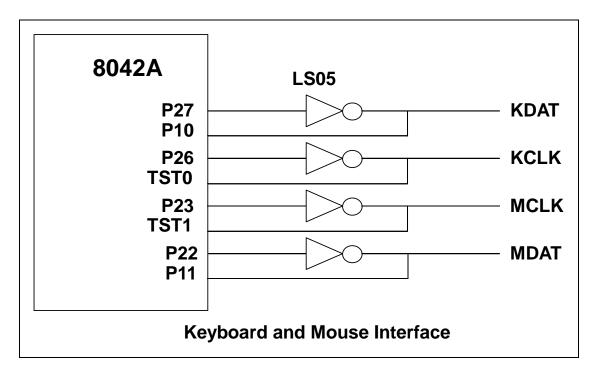

- Four Open Drain Outputs Dedicated for Keyboard/Mouse Interface

- Asynchronous Access to Two Data Registers and One Status Register

- Supports Interrupt and Polling Access

- 8 Bit Counter Timer

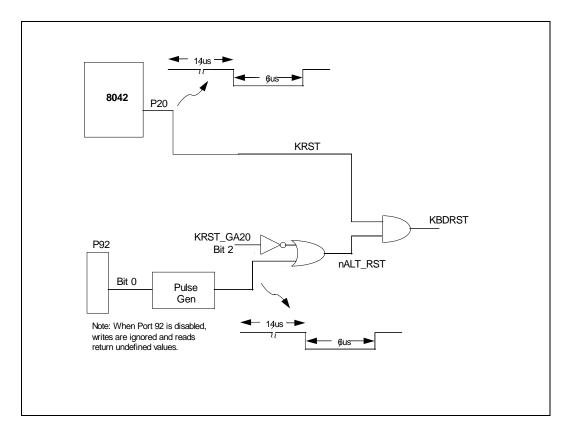

- Port 92 Support

- Fast Gate A20 and KRESET Outputs

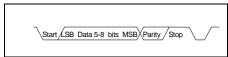

- Serial Ports

- Two Full Function Serial Ports

- High Speed NS16C550A Compatible UARTs with Send/Receive 16-Byte FIFOs

- Supports 230k and 460k Baud Programmable Baud Rate Generator Modem Control Circuitry

- 480 Address and 15 IRQ Options

- Infrared Port

- Multiprotocol Infrared Interface

- 32-Byte Data FIFO

- IrDA 1.0 Compliant

- Consumer IR

- SHARP ASK IR

- 480 Address, Up to 15 IRQ and Three DMA Options

- Multi-Mode<sup>™</sup> Parallel Port with ChiProtect<sup>™</sup>

- Standard Mode IBM PC/XT<sup>®</sup>, PC/AT<sup>®</sup>, and PS/2™ Compatible Bidirectional Parallel Port

- Enhanced Parallel Port (EPP)

Compatible EPP 1.7 and EPP 1.9

(IEEE 1284 Compliant)

- IEEE 1284 Compliant Enhanced Capabilities Port (ECP)

- ChiProtect Circuitry for Protection

- 960 Address, Up to 15 IRQ and Three DMA Options

- LPC Interface

- Multiplexed Command, Address and Data Bus

- Serial IRQ Interface Compatible with Serialized IRQ Support for PCI Systems

- PME Interface

- 100 Pin QFP Lead-Free RoHS Compliant Package

## ORDERING INFORMATION

Order Number(s):

LPC47B272QFP for 100 pin QFP package

LPC47B272-MS for 100 pin QFP Lead-Free RoHS Compliant Package

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright © 2007 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomally sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

## **TABLE OF CONTENTS**

| FEATURES                                                | 1                                     |

|---------------------------------------------------------|---------------------------------------|

| GENERAL DESCRIPTION                                     |                                       |

| PIN CONFIGURATION                                       |                                       |

| DESCRIPTION OF PIN FUNCTIONS                            |                                       |

| Buffer Type Descriptions                                | 12                                    |

| PINS THAT REQUIRE EXTERNAL PULLUP RESISTORS             |                                       |

| BLOCK DIAGRAM                                           | 13                                    |

| REFERENCE DOCUMENTS                                     | 13                                    |

| 3 VOLT OPERATION / 5 VOLT TOLERANCE                     | 13                                    |

| POWER FUNCTIONALITY                                     | 14                                    |

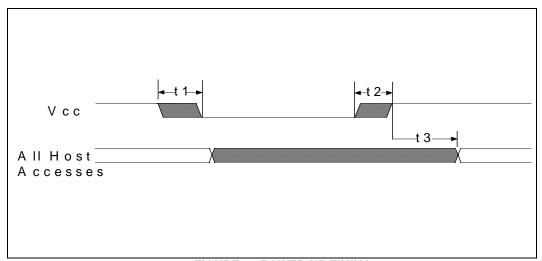

| VCC Power                                               | 14                                    |

| VTR SUPPORT                                             |                                       |

| INTERNAL PWRGOOD                                        |                                       |

| 32.768 KHz Trickle Clock InputIndication of 32kHz Clock |                                       |

| TRICKLE POWER FUNCTIONALITY                             |                                       |

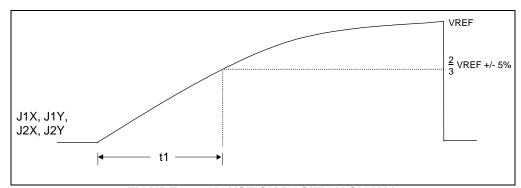

| VREF PIN                                                | 16                                    |

| MAXIMUM CURRENT VALUES                                  |                                       |

| POWER MANAGEMENT EVENTS (PME/SCI)                       |                                       |

|                                                         |                                       |

| SUPER I/O REGISTERSHOST PROCESSOR INTERFACE (LPC)       |                                       |

| LPC INTERFACE                                           |                                       |

| FLOPPY DISK CONTROLLER                                  |                                       |

| FDC INTERNAL REGISTERS                                  | 22                                    |

| COMMAND SET/DESCRIPTIONS                                | 36                                    |

| INSTRUCTION SET                                         | 38                                    |

| FDC SWAP BIT                                            |                                       |

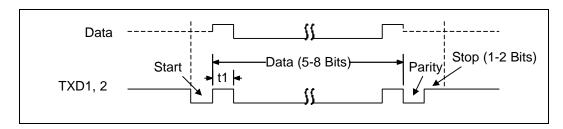

| SERIAL PORT (UART)                                      | 55                                    |

| INFRARED INTERFACE                                      | 68                                    |

| IR Transmit Pins                                        | 68                                    |

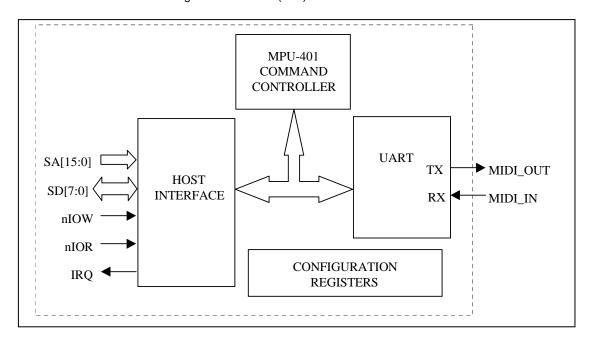

| MPU-401 MIDI UART                                       | 69                                    |

| Overview                                                | 60                                    |

| HOST INTERFACE                                          | · · · · · · · · · · · · · · · · · · · |

| MPU-401 COMMAND CONTROLLER                              | 72                                    |

| MIDI UART                                               |                                       |

| MPU-401 Configuration Registers                         | 73                                    |

**DATASHEET**

| PARALLEL PORT                                                                         | 74       |

|---------------------------------------------------------------------------------------|----------|

| IBM XT/AT COMPATIBLE, BI-DIRECTIONAL AND EPP MODESEXTENDED CAPABILITIES PARALLEL PORT | 75<br>79 |

| PARALLEL PORT FLOPPY DISK CONTROLLER                                                  | 90       |

| FDC SWAP BIT                                                                          | 90       |

| FLOPPY ON PARALLEL PORT PIN                                                           | 92       |

| POWER MANAGEMENT                                                                      | 93       |

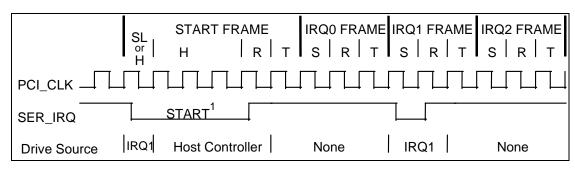

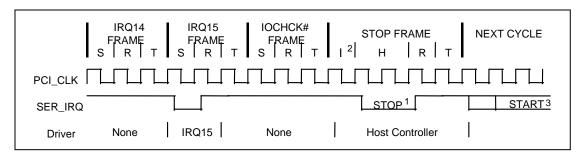

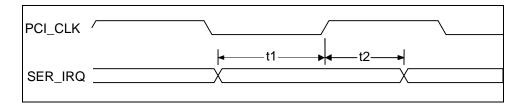

| SERIAL IRQ                                                                            | 96       |

| TIMING DIAGRAMS FOR SER_IRQ CYCLE                                                     | 96       |

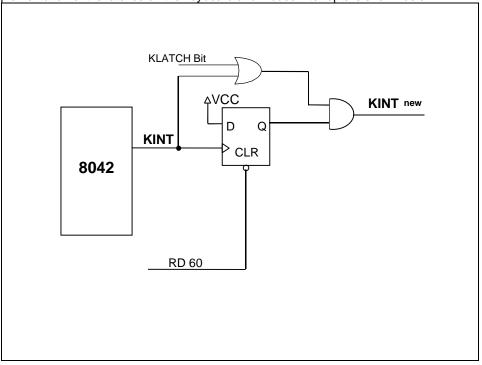

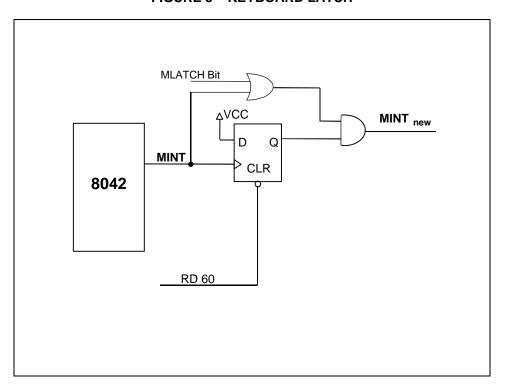

| 8042 KEYBOARD CONTROLLER DESCRIPTION                                                  | 99       |

| LATCHES ON KEYBOARD AND MOUSE IRQS<br>KEYBOARD AND MOUSE PME GENERATION               |          |

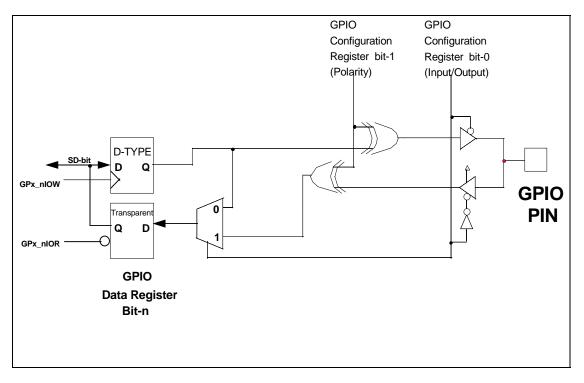

| GENERAL PURPOSE I/O                                                                   | 108      |

| GPIO PINS EITHER EDGE TRIGGERED INTERRUPTS LED FUNCTIONALITY WATCH DOG TIMER          | 113      |

| SYSTEM MANAGEMENT INTERRUPT (SMI)                                                     | 114      |

| PME SUPPORT                                                                           | 116      |

| 'WAKE ON SPECIFIC KEY' OPTION                                                         | 117      |

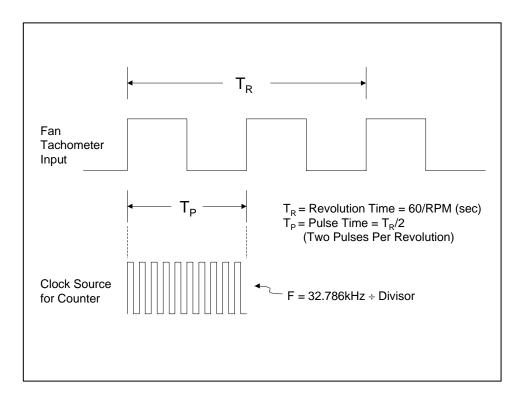

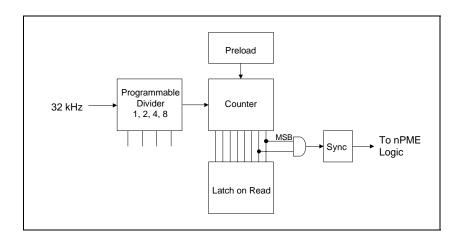

| FAN SPEED CONTROL AND MONITORING                                                      | 119      |

| FAN SPEED CONTROLFAN TACHOMETER INPUTS                                                |          |

| SECURITY FEATURE                                                                      | 123      |

| GPIO DEVICE DISABLE REGISTER CONTROL                                                  |          |

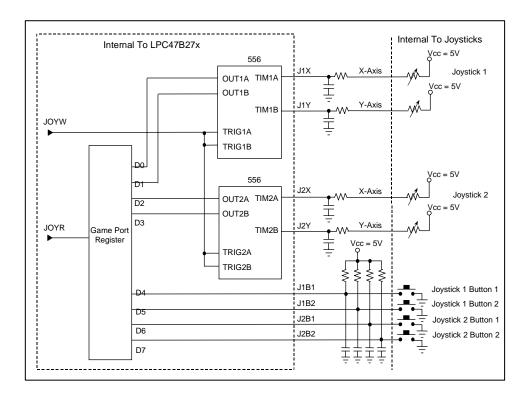

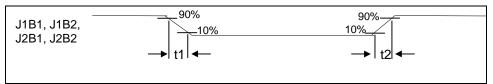

| GAME PORT LOGIC                                                                       | 123      |

| Power Control Register                                                                |          |

| ISA IRQ TO SERIAL IRQ CONVERSION CAPABILITY                                           | 126      |

| RUNTIME REGISTERS                                                                     | 127      |

| CONFIGURATION                                                                         | 150      |

| OPERATIONAL DESCRIPTION                                                               | 167      |

| MAXIMUM GUARANTEED RATINGS*                                                           |          |

| DC ELECTRICAL CHARACTERISTICS                                                         |          |

| TIMING DIAGRAMS                                                                       | 170      |

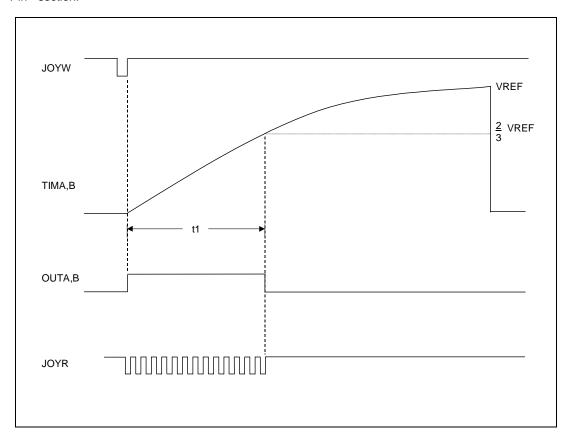

| FIGURE 31 – JOYSTICK POSITION SIGNAL | 189      |

|--------------------------------------|----------|

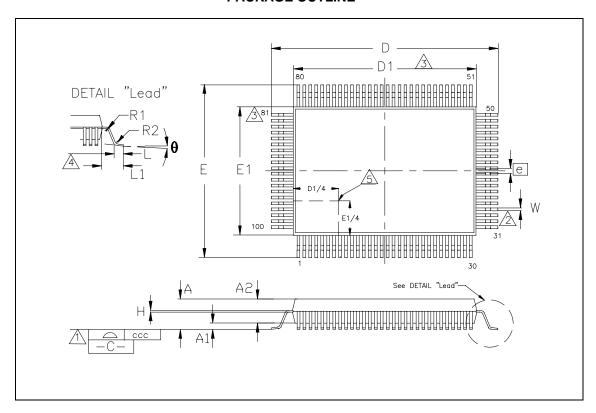

| PACKAGE OUTLINE                      | 193      |

| APPENDIX - TEST MODE                 | 194      |

| ATTEMPIX - TEST MODE                 | ·····1)7 |

| BOARD TEST MODE                      | 194      |

## **GENERAL DESCRIPTION**

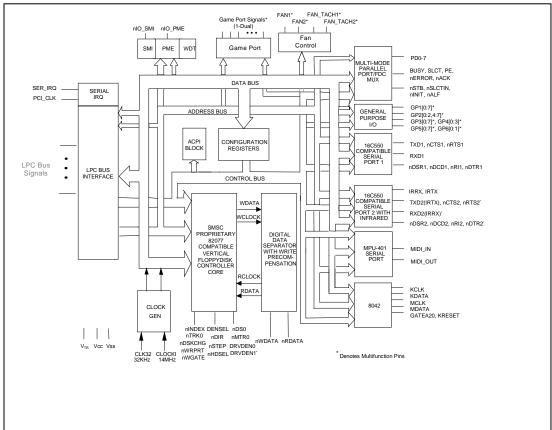

The LPC47B27x\* is a 3.3V PC98/PC99 compliant Super I/O controller. The LPC47B27x implements the LPC interface, a pin reduced ISA bus interface which provides the same or better performance as the ISA/X-bus with a substantial savings in pins used. The LPC47B27x provides fan control through two fan speed control output pins and two fan tachometer input pins. It also provides 37 general purpose input/output (GPIO) pins, a dual game port interface, MPU-401 MIDI support and ISA IRQ to Serial IRQ conversion.

The LPC47B27x incorporates a keyboard interface, SMSC's true CMOS 765B floppy disk controller, advanced digital data separator, two 16C550A compatible UARTs, one Multi-Mode parallel port which includes ChiProtect circuitry plus EPP and ECP, on-chip 12 mA AT bus drivers, one floppy direct drive support, and Intelligent Power Management including PME support. The true CMOS 765B core provides 100% compatibility with IBM PC/XT and PC/AT architectures in addition to providing data overflow and underflow protection. The SMSC advanced digital data separator incorporates SMSC's patented data separator technology, allowing for ease of testing and use. Both on-chip UARTs are compatible with the NS16C550A. The parallel port is compatible with IBM PC/AT architecture, as well as IEEE 1284 EPP and ECP. The LPC47B27x incorporates sophisticated power control circuitry (PCC) which includes support for keyboard, mouse and consumer infrared wake-up events. The PCC supports multiple low power-down modes.

The LPC47B27x supports the ISA Plug-and-Play Standard register set (Version 1.0a) and provides the recommended functionality to support Windows '95. The I/O Address, DMA Channel and hardware IRQ of each logical device in the LPC47B27x may be reprogrammed through the internal configuration registers. There are 480 (960 for Parallel Port) I/O address location options, a Serialized IRQ interface, and three DMA channels.

The LPC47B27x does not require any external filter components and is therefore easy to use and offers lower system costs and reduced board area. The LPC47B27x is software and register compatible with SMSC's proprietary 82077AA core.

\*The "x" in the part number is a designator that changes depending upon the particular BIOS used inside the specific chip. "2" denotes AMI Keyboard BIOS and "7" denotes Phoenix 42i Keyboard BIOS.

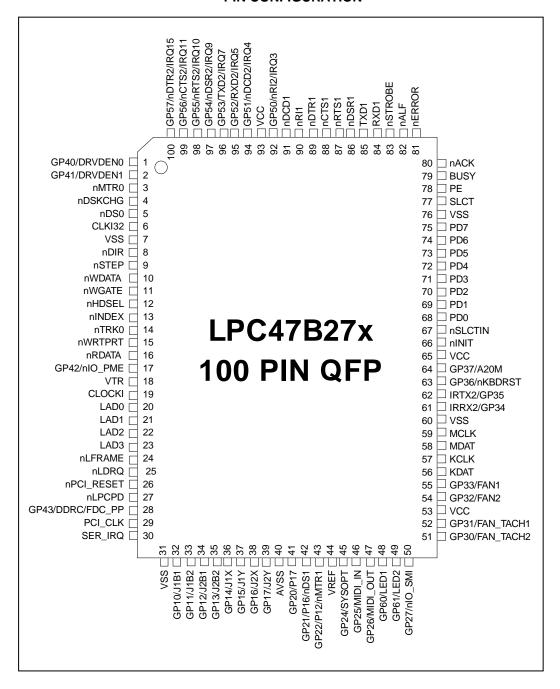

## **PIN CONFIGURATION**

| B.I.               | DESCRIPTION OF PIN FUNCTIONS                |          |                    |                  |                                   |           |  |  |

|--------------------|---------------------------------------------|----------|--------------------|------------------|-----------------------------------|-----------|--|--|

| PIN<br>No./<br>QFP | NAME                                        | TOTAL    | SYMBOL             | BUFFER<br>TYPE   | BUFFER TYPE PER FUNCTION (NOTE 1) | NOTE<br>S |  |  |

|                    | PROC                                        | ESSOR/HO | OST LPC INTER      | <b>FACE (10)</b> |                                   |           |  |  |

| 23:20              | Multiplexed Command,<br>Address, Data [3:0] | 4        | LAD[3:0]           | PCI_IO           | PCI_IO                            |           |  |  |

| 24                 | Frame                                       | 1        | nLFRAME            | PCI_I            | PCI_I                             |           |  |  |

| 25                 | Encoded DMA Request                         | 1        | nLDRQ              | PCI_O            | PCI_O                             |           |  |  |

| 26                 | PCI Reset                                   | 1        | nPCI_RESE<br>T     | PCI_I            | PCI_I                             |           |  |  |

| 27                 | Power Down                                  | 1        | nLPCPD             | PCI_I            | PCI_I                             | 2         |  |  |

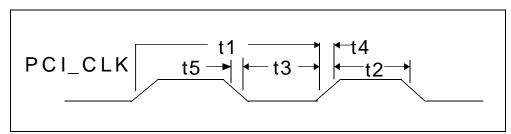

| 29                 | PCI Clock                                   | 1        | PCI_CLK            | PCI_ICL<br>K     | PCI_ICLK                          |           |  |  |

| 30                 | Serial IRQ                                  | 1        | SER_IRQ            | PCI_IO           | PCI_IO                            |           |  |  |

|                    |                                             | С        | LOCKS (2)          | •                |                                   |           |  |  |

| 6                  | 32.768kHz Trickle<br>Clock Input            | 1        | CLOCKI32           | IS               | IS                                | 3         |  |  |

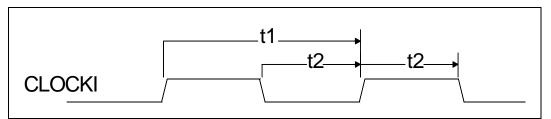

| 19                 | 14.318MHz Clock Input                       | 1        | CLOCKI             | IS               | IS                                |           |  |  |

|                    |                                             | FAN      | CONTROL (4)        |                  |                                   |           |  |  |

| 51                 | General Purpose I/O<br>/Fan Tachometer 2    | 1        | GP30/<br>FAN_TACH2 | IO8              | (I/O8/OD8)/I                      |           |  |  |

| 52                 | General Purpose I/O<br>/Fan Tachometer 1    | 1        | GP31/<br>FAN_TACH1 | IO8              | (I/O8/OD8)/I                      |           |  |  |

| 54                 | General Purpose I/O<br>/Fan Speed Control 2 | 1        | GP32/FAN2          | IO12             | (I/O12/OD12)/<br>(O12/OD12)       | 4         |  |  |

| 55                 | General Purpose I/O /Fan Speed Control 1    | 1        | GP33/FAN1          | IO12             | (I/O12/OD12)/<br>(O12/OD12)       | 4         |  |  |

|                    | 71 dil opood coniioi i                      | INFRARE  | D INTERFACE        | (2)              | ( /                               |           |  |  |

| 61                 | Infrared Rx<br>/General Purpose I/O         | 1        | IRRX2/GP34         | IS/O8            | IS/(IS/O8/OD8)                    |           |  |  |

| 62                 | Infrared Tx<br>/General Purpose I/O         | 1        | IRTX2/GP35         | IO12             | O12/(I/O12/<br>OD12)              | 5,6       |  |  |

|                    | , , , , , , , , , , , , , , , , , , , ,     | POW      | /ER PINS (10)      | 1                | ,                                 |           |  |  |

| 53,<br>65,93       | +3.3 Volt Supply<br>Voltage                 | 3        | VCC                |                  |                                   |           |  |  |

| 7, 31,<br>60,76    | Ground                                      | 4        | VSS                |                  |                                   |           |  |  |

| 40                 | Analog Ground                               | 1        | AVSS               |                  |                                   |           |  |  |

| 44                 | Reference Voltage                           | 1        | VREF               |                  |                                   |           |  |  |

| 18                 | +3.3 Volt Standby<br>Supply Voltage         | 1        | VTR                |                  |                                   | 8         |  |  |

|                    | FDD INTERFACE (14)                          |          |                    |                  |                                   |           |  |  |

| 16                 | Read Disk Data                              | 1        | nRDATA             | IS               | IS                                |           |  |  |

| 11                 | Write Gate                                  | 1        | nWGATE             | 012              | (O12/OD12)                        |           |  |  |

| 10                 | Write Disk Data                             | 1        | nWDATA             | 012              | (O12/OD12)                        |           |  |  |

| 12                 | Head Select                                 | 1        | nHDSEL             | 012              | (O12/OD12)                        |           |  |  |

| 8                  | Step Direction                              | 1        | nDIR               | 012              | (O12/OD12)                        |           |  |  |

| 9                  | Step Pulse                                  | 1        | nSTEP              | 012              | (O12/OD12)                        |           |  |  |

| 4                  | Disk Change                                 | 1        | nDSKCHG            | IS               | IS                                |           |  |  |

| 5                  | Drive Select 0                              | 1        | nDS0               | 012              | (O12/OD12)                        |           |  |  |

| 3                  | Motor On 0                                  | 1        | nMTR0              | 012              | (O12/OD12)                        |           |  |  |

| 15                 | Write Protected                             | 1        | nWRTPRT            | IS               | is                                |           |  |  |

|                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1              | BUEEED TYDE                 |           |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|-----------|

| NAME                                                    | TOTAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SYMBOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | BUFFER<br>TYPE | PER<br>FUNCTION<br>(NOTE 1) | NOTE<br>S |

|                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |                             |           |

| Index Pulse Input                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IS             |                             |           |

| General Purpose<br>I/O/Drive Density<br>Select 0        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GP40/<br>DRVDEN0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IO12           | (I/O12/OD12)/<br>(O12/OD12) |           |

| General Purpose<br>I/O/Drive Density<br>Select 1        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GP41/<br>DRVDEN1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IO12           | (I/O12/OD12)/<br>(O12/OD12) |           |

|                                                         | SERIAL PO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RT 1 INTERFAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CE (8)         |                             | _         |

| Receive Serial Data 1                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | RXD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IS             | IS                          |           |

| Transmit Serial Data 1                                  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TXD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | O12            | O12                         | 12        |

| Request to Send 1                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nRTS1/<br>SYSOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | O8             | O8                          |           |

|                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nCTS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I              | 1                           |           |

| Data Terminal Ready 1                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nDTR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | O6             | O6                          |           |

| Data Set Ready 1                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nDSR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1              | 1                           |           |

| Data Carrier Detect 1                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nDCD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1              | I                           |           |

| Ring Indicator 1                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nRI1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I              | I                           |           |

| Ç                                                       | SERIAL PO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RT 2 INTERFAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CE (8)         |                             | •         |

| General Purpose I/O<br>/Receive Serial Data 2<br>/IRQ5  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GP52/RXD2/<br>IRQ5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IS/O8          | (IS/O8/OD8)/<br>IS/IS       |           |

| General Purpose I/O<br>/Transmit Serial Data 2<br>/IRQ7 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GP53/TXD2/<br>IRQ7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IO12           | (I/O12/OD12)/<br>O12/I      | 5,6,7     |

| General Purpose I/O<br>/Request to Send<br>2/IRQ10      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GP55/<br>nRTS2/<br>IRQ10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IO8            | (I/O8/OD8)/<br>O8/I         |           |

| General Purpose I/O<br>/Clear to Send 2/IRQ11           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GP56/nCTS<br>2/IRQ11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IO8            | (I/O8/OD8)/I/I              |           |

| General Purpose I/O<br>/Data Terminal<br>Ready/IRQ15    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GP57/nDTR<br>2/IRQ15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IO8            | (I/O8/OD8)/<br>O8/I         |           |

| General Purpose I/O<br>/Data Set Ready<br>2/IRQ9        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GP54/nDSR<br>2/IRQ9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IO8            | (I/O8/OD8)/I/I              |           |

| General Purpose<br>I/O/Data Carrier Detect<br>2/IRQ4    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GP51/<br>nDCD2/<br>IRQ4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IO8            | (I/O8/OD8)/I/I              |           |

| General Purpose<br>I/O/Ring Indicator<br>2/IRQ3         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GP50/nRI2/<br>IRQ3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IO8            | (I/O8/OD8)/I/I              |           |

| PA                                                      | ARALLEL P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CE (17)        |                             |           |

| Initiate Output/FDC                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nINIT /nDIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | OP14           | (OD14/OP14)/                |           |

| Direction Control                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                | OD14                        |           |

| Direction Control Printer Select Input/FDC Step Pulse   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nSLCTIN<br>/nSTEP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OP14           | (OD14/OP14)/<br>OD14        |           |

| Direction Control Printer Select                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | OP14           | (OD14/OP14)/                |           |

|                                                         | Index Pulse Input General Purpose I/O/Drive Density Select 0 General Purpose I/O/Drive Density Select 1  Receive Serial Data 1 Transmit Serial Data 1 Transmit Serial Data 1 Request to Send 1  Data Terminal Ready 1 Data Carrier Detect 1 Ring Indicator 1  General Purpose I/O /Receive Serial Data 2 /IRQ5  General Purpose I/O /Transmit Serial Data 2 /IRQ7  General Purpose I/O /Request to Send 2/IRQ10  General Purpose I/O /Clear to Send 2/IRQ11  General Purpose I/O /Clear to Send 2/IRQ11  General Purpose I/O /Data Terminal Ready/IRQ15  General Purpose I/O /Data Set Ready 2/IRQ9  General Purpose I/O/Data Set Ready 2/IRQ9  General Purpose I/O/Data Carrier Detect 2/IRQ4  General Purpose I/O/Ring Indicator 2/IRQ3 | NAME  Track 0 Index Pulse Input General Purpose I/O/Drive Density Select 0 General Purpose I/O/Drive Density Select 1  SERIAL PO Receive Serial Data 1 Transmit Serial Data 1 Transmit Serial Data 1 Tabata Terminal Ready 1 Data Set Ready 1 Data Carrier Detect 1 Ring Indicator 1 Transmit Serial Data 2 I/RQ5 General Purpose I/O I/Receive Serial Data 2 I/RQ7 General Purpose I/O I/Request to Send 2/IRQ7 General Purpose I/O I/Request to Send 2/IRQ10 General Purpose I/O I/Clear to Send 2/IRQ11 General Purpose I/O I/Data Terminal Ready/IRQ15 General Purpose I/O I/Data Set Ready 2/IRQ9 General Purpose I/O/Data Carrier Detect 2/IRQ4 General Purpose I/O/Ring Indicator 2/IRQ3 PARALLEL F | NAME           | Track 0                     | NAME      |

| PIN         | DESCRIPTION OF PIN FUNCTIONS  BUFFER TYPE   |          |                   |                |                             |           |

|-------------|---------------------------------------------|----------|-------------------|----------------|-----------------------------|-----------|

| No./<br>QFP | NAME                                        | TOTAL    | SYMBOL            | BUFFER<br>TYPE | PER<br>FUNCTION<br>(NOTE 1) | NOTE<br>S |

| 70          | Port Data 2/FDC Write<br>Protected          | 1        | 1 PD2 IS          |                | IOP14/IS                    |           |

| 71          | Port Data 3/FDC Read<br>Disk Data           | 1        | PD3<br>/nRDATA    | IS/OP14        | IOP14/IS                    |           |

| 72          | Port Data 4/FDC Disk<br>Change              | 1        | PD4<br>/nDSKCHG   | IS/OP14        | IOP14/IS                    |           |

| 73          | Port Data 5                                 | 1        | PD5               | IOP14          | IOP14                       |           |

| 74          | Port Data 6/<br>FDC Motor On 0              | 1        | PD6/nMTR0         | IOP14          | IOP14/OD14                  |           |

| 75          | Port Data 7                                 | 1        | PD7               | IOP14          | IOP14                       |           |

| 77          | Printer Selected<br>Status/FDC Write Gate   | 1        | SLCT<br>/nWGATE   | IO12           | I/OD12                      |           |

| 78          | Paper End/FDC Write<br>Data                 | 1        | PE<br>/nWDATA     | IO12           | I/OD12                      |           |

| 79          | Busy/FDC Motor On                           | 1        | BUSY<br>/nMTR1    | IO12           | I/OD12                      |           |

| 80          | Acknowledge/FDC<br>Drive Select 1           | 1        | nACK /nDS1        | I/OD12         | I/OD12                      |           |

| 81          | Error/FDC Head Select                       | 1        | nERROR<br>/nHDSEL | IO12           | I/OD12                      |           |

| 82          | Autofeed Output/FDC<br>Density Select       | 1        | nALF<br>/nDRVDEN0 | OP14           | (OD14/OP14)/<br>OD14        |           |

| 83          | Strobe Output/FDC<br>Drive Select           | 1        | nSTROBE<br>/nDS0  | OP14           | (OD14/OP14)/<br>OD14        |           |

|             |                                             | YBOARD/N | OUSE INTERF       |                |                             |           |

| 56          | Keyboard Data                               | 1        | KDAT              | IOD16          | IOD16                       |           |

| 57          | Keyboard Clock                              | 1        | KCLK              | IOD16          | IOD16                       |           |

| 58          | Mouse Data                                  | 1        | MDAT              | IOD16          | IOD16                       |           |

| 59          | Mouse Clock                                 | 1        | MCLK              | IOD16          | IOD16                       |           |

| 63          | General Purpose I/O /Keyboard Reset         | 1        | GP36/<br>nKBDRST  | IO8            | (I/O8/OD8)/<br>O8           | 10        |

| 64          | General Purpose I/O<br>/Gate A20            | 1        | GP37/A20M         | IO8            | (I/O8/OD8)/<br>O8           | 10        |

|             | 1                                           | GENERAL  | PURPOSE I/O       | (19)           | 1                           |           |

| 32          | General Purpose I/O /Joystick 1 Button 1    | 1        | GP10/J1B1         | IS/O8          | (IS/O8/OD8)/<br>IS          |           |

| 33          | General Purpose I/O<br>/Joystick 1 Button 2 | 1        | GP11/J1B2         | IS/O8          | (IS/O8/OD8)/<br>IS          |           |

| 34          | General Purpose I/O<br>/Joystick 2 Button 1 | 1        | GP12/J2B1         | IS/O8          | (IS/O8/OD8)/<br>IS          |           |

| 35          | General Purpose I/O<br>/Joystick 2 Button 2 | 1        | GP13/J2B2         | IS/O8          | (IS/O8/OD8)/<br>IS          |           |

| 36          | General Purpose I/O<br>/Joystick 1 X-Axis   | 1        | GP14/J1X          | IO12           | (I/O12/ OD12)/<br>IO12      |           |

| 37          | General Purpose I/O<br>/Joystick 1 Y-Axis   | 1        | GP15/J1Y          | IO12           | (I/O12/ OD12)/<br>IO12      |           |

| 38          | General Purpose I/O<br>/Joystick 2 X-Axis   | 1        | GP16/J2X          | IO12           | (I/O12/<br>OD12)/IO12       |           |

| 39          | General Purpose I/O<br>/Joystick 2 Y-Axis   | 1        | GP17/J2Y          | IO12           | (I/O12/<br>OD12)/IO12       |           |

| PIN<br>No./<br>QFP | NAME                                                                    | TOTAL | SYMBOL               | BUFFER<br>TYPE | BUFFER TYPE<br>PER<br>FUNCTION       | NOTE |

|--------------------|-------------------------------------------------------------------------|-------|----------------------|----------------|--------------------------------------|------|

|                    | NAME                                                                    | IOIAL | STWIDOL              |                | (NOTE 1)                             | S    |

| 41                 | General Purpose I/O /<br>P17                                            | 1     | GP20/P17             | IO8            | (I/O8/OD8)/<br>IO8                   |      |

| 42                 | General Purpose I/O /<br>P16 /nDS1                                      | 1     | GP21 /P16/<br>nDS1   | IO12           | (I/O12/OD12)/<br>IO12/(O12/<br>OD12) |      |

| 43                 | General Purpose I/O /<br>P12/nMTR1                                      | 1     | GP22 /P12/<br>nMTR1  | IO12           | (I/O12/<br>OD12)/IO12/<br>(O12/OD12) |      |

| 45                 | General Purpose I/O /<br>System Option                                  | 1     | GP24<br>/SYSOPT      | IO8            | (I/O8/OD8)                           | 9    |

| 46                 | General Purpose I/O<br>/MIDI_IN                                         | 1     | GP25<br>/MIDI_IN     | IO8            | (I/O8/OD8)/I                         |      |

| 47                 | General Purpose I/O<br>/MIDI_OUT                                        | 1     | GP26<br>/MIDI_OUT    | IO12           | (I/O12/OD12)/<br>O12                 |      |

| 50                 | General Purpose I/O<br>/SMI Output                                      | 1     | GP27<br>/nIO_SMI     | IO12           | (I/O12/OD12)/<br>OD12                |      |

| 48                 | General Purpose I/O /<br>LED                                            | 1     | GP60 /LED1           | IO12           | (I/O12/OD12)/<br>O12                 | 11   |

| 49                 | General Purpose I/O /<br>LED                                            | 1     | GP61 /LED2           | IO12           | (I/O12/OD12)/<br>O12                 | 11   |

| 17                 | General Purpose I/O /<br>Power Management<br>Event                      | 1     | GP42<br>/nIO_PME     | IO12           | (I/O12/OD12)/<br>OD12                |      |

| 28                 | General Purpose I/O /Device Disable Reg. Control / FDC on Parallel Port | 1     | GP43/DDRC<br>/FDC_PP | IO8            | (I/O8/OD8)/I/I                       |      |

- Note: The "n" as the first letter of a signal name indicates an "Active Low" signal.

- Note 1: Buffer types per function on multiplexed pins are separated by a slash "/". Buffer types in parenthesis represent multiple buffer types for a single pin function.

- Note 2: The nLPCPD pin may be tied high. The LPC interface will function properly if the nPCI\_RESET signal follows the protocol defined for the nLRESET signal in the "Low Pin Count Interface Specification".

- Note 3: If the 32kHz input clock is not used the CLKI32 pin must be grounded. There is a bit in the configuration register at 0xF0 in Logical Device A that indicates whether or not the 32kHz clock is connected. This bit determines the clock source for the fan tachometer, LED and "wake on specific key" logic. Set this bit to '1' if the clock is not connected.

- Note 4. The fan control pins (FAN1 and FAN2) come up as outputs and low following a VCC POR and Hard Reset.

- Note 5: The IRTX pins (IRTX2/GP35 and GP53/TXD2) are driven low when the part is powered by VTR (VCC=0V with VTR=3.3V). The IRTX2/GP35 pin will remain low following a power-up (VCC POR) until serial port 2 is enabled by setting the activate bit, at which time the pin will reflect the state of the IR transmit output of the IRCC block. The GP53/TXD2 pin will remain low following a VCC POR until the TXD2 function is selected for the pin and serial port is enabled by setting the activate bit, at which time the pin will reflect the state of the IR transmit output of the IRCC block (if IR is enabled).

- Note 6:The "activate" bit for the CIrCC is reset by VTR POR only. The  $V_{CC}$  power-up default for this pin is Logic "0" if the IRTX2 function is programmed on the GPIO.

- Note 7:The "activate" bit for Serial Port 2 is reset by VTR POR only. The V<sub>CC</sub> power-up default for this pin is Logic "0" if the TXD2 function is programmed on the GPIO.

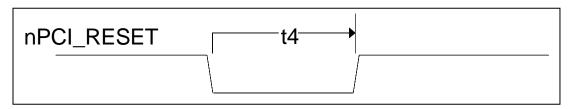

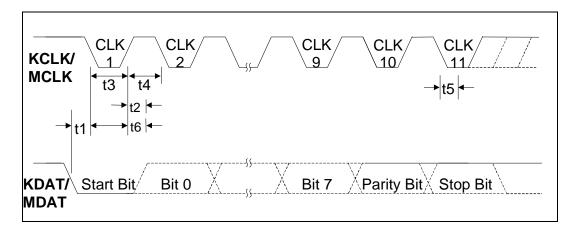

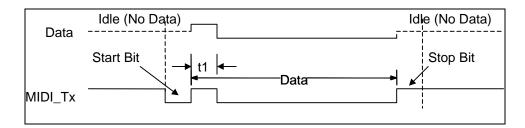

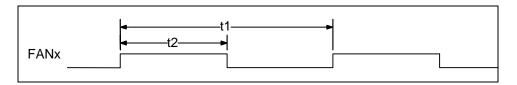

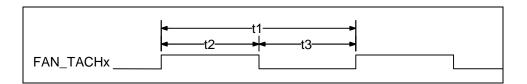

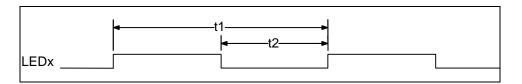

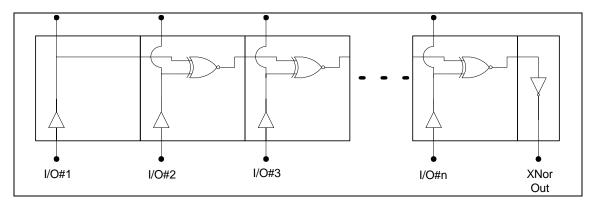

- Note 8: VTR can be connected to VCC if no wakeup functionality is required.