# High Efficiency Bidirectional Multicell Battery Balancer

# **FEATURES**

- Bidirectional Synchronous Flyback Balancing of Up to 6 Li-lon or LiFePO<sub>4</sub> Cells in Series

- Up to 10A Balancing Current (Set by Externals)

- Integrates Seamlessly with the LTC680x Family of Multicell Battery Stack Monitors

- Bidirectional Architecture Minimizes Balancing Time and Power Dissipation

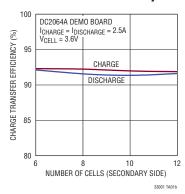

- Up to 92% Charge Transfer Efficiency

- Stackable Architecture Enables >1000V Systems

- Uses Simple 2-Winding Transformers

- 1MHz Daisy-Chainable Serial Interface with 4-Bit CRC Packet Error Checking

- High Noise Margin Serial Communication

- Numerous Fault Protection Features

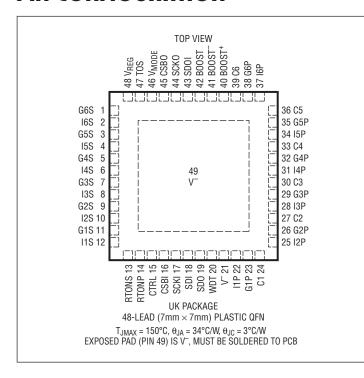

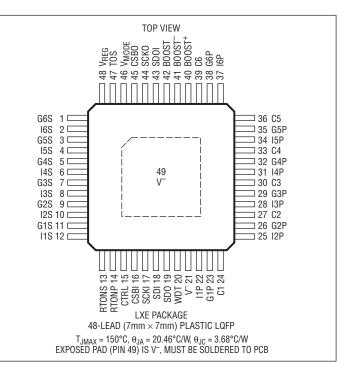

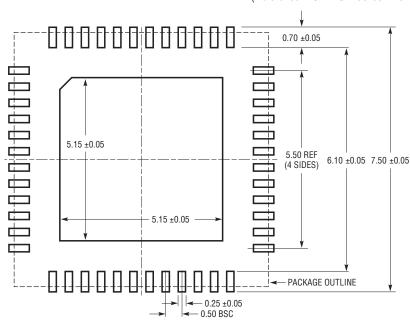

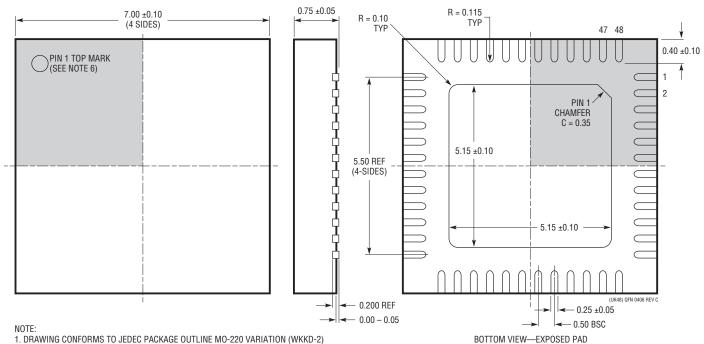

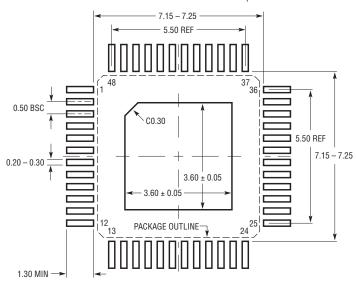

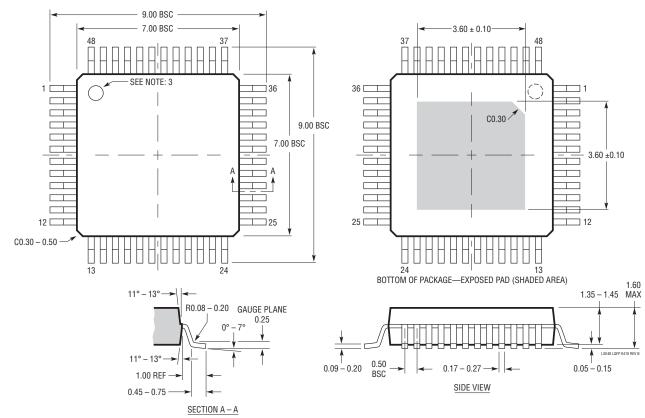

- 48-Lead Exposed Pad QFN and LQFP Packages

# **APPLICATIONS**

- Electric Vehicles/Plug-in HEVs

- High Power UPS/Grid Energy Storage Systems

- General Purpose Multicell Battery Stacks

∠7, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and isoSPI is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

# DESCRIPTION

The LTC®3300-1 is a fault-protected controller IC for transformer-based bidirectional active balancing of multicell battery stacks. All associated gate drive circuitry, precision current sensing, fault detection circuitry and a robust serial interface with built-in watchdog timer are integrated.

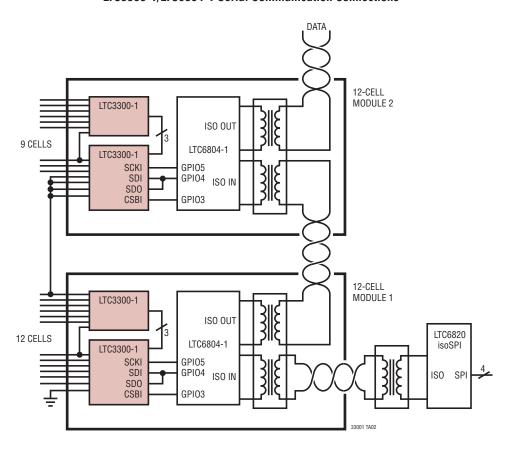

Each LTC3300-1 can balance up to 6 series-connected battery cells with an input common mode voltage up to 36V. Charge from any selected cell can be transferred at high efficiency to or from 12 or more adjacent cells. A unique level-shifting SPI-compatible serial interface enables multiple LTC3300-1 devices to be connected in series, without opto-couplers or isolators, allowing for balancing of every cell in a long string of series-connected batteries.

When multiple LTC3300-1 devices are connected in series they can operate simultaneously, permitting all cells in the stack to be balanced concurrently and independently. Fault protection features include readback capability, cyclic redundancy check (CRC) error detection, maximum on-time volt-second clamps, and overvoltage shutoffs.

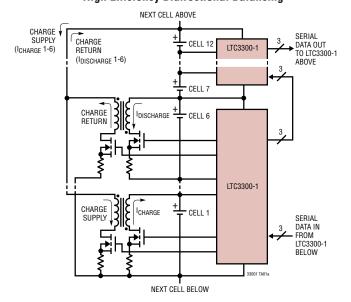

# TYPICAL APPLICATION

#### **High Efficiency Bidirectional Balancing**

#### **Balancer Efficiency**

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Total Supply Voltage (C6 to V <sup>-</sup> ) | 36V                              |

|----------------------------------------------|----------------------------------|

| Input Voltage (Relative to V <sup>-</sup> )  |                                  |

| C1                                           | 0.3V to 6V                       |

| I1P                                          | 0.3V to 0.3V                     |

| I1S, I2S, I3S, I4S, I5S, I6S                 | 0.3V to 0.3V                     |

| CSBI, SCKI, SDI                              | 0.3V to 6V                       |

| CSBO, SCKO, SDOI                             | 0.3V to 36V                      |

| V <sub>REG</sub> , SDO                       |                                  |

| RTONP, RTONS0.3V to                          | Min[V <sub>REG</sub> + 0.3V, 6V] |

| TOS, V <sub>MODE</sub> , CTRL,               |                                  |

| BOOST, WDT0.3V to                            | $Min[V_{REG} + 0.3V, 6V]$        |

| Voltage Between Pins              |                   |

|-----------------------------------|-------------------|

| C <i>n</i> to C <i>n-1</i> *      | 0.3V to 6V        |

| I <i>n</i> P to C <i>n-1*</i>     | 0.3V to 0.3V      |

| BOOST+ to C6                      | 0.3V to 6V        |

| CSBO to SCKO, CSBO to SDOI,       |                   |

| SCKO to SDOI                      | 0.3V to 0.3V      |

| SDO Current                       | 10mA              |

| G1P, GnP, G1S, GnS, BOOST Curre   | ent ±200mA        |

| Operating Junction Temperature Ra | ange (Notes 2, 7) |

| LTC3300I-1                        | 40°C to 125°C     |

| LTC3300H-1                        | 40°C to 150°C     |

| Storage Temperature Range         |                   |

| *n = 2 to 6                       |                   |

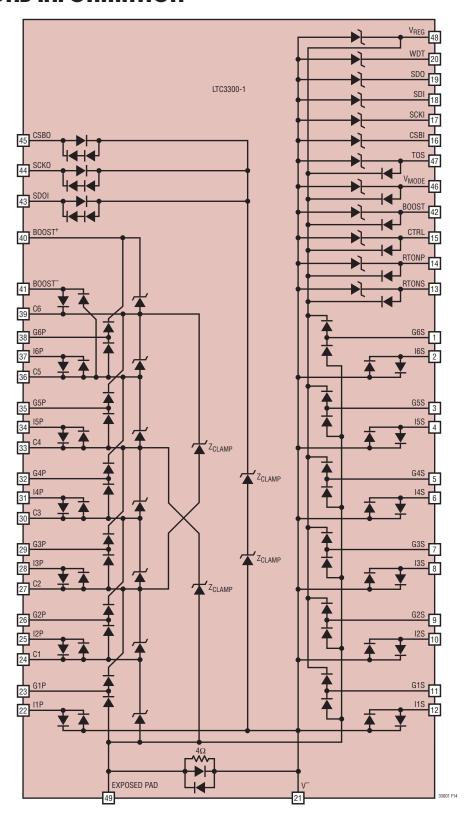

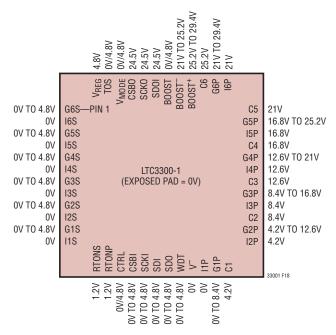

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION               | TEMPERATURE RANGE |

|-------------------|--------------------|---------------|-----------------------------------|-------------------|

| LTC3300IUK-1#PBF  | LTC3300IUK-1#TRPBF | LTC3300UK-1   | 48-Lead (7mm × 7mm) Plastic QFN   | -40°C to 125°C    |

| LTC3300HUK-1#PBF  | LTC3300HUK-1#TRPBF | LTC3300UK-1   | 48-Lead (7mm × 7mm) Plastic QFN   | -40°C to 150°C    |

| LEAD FREE FINISH  | TRAY               | PART MARKING* | PACKAGE DESCRIPTION               | TEMPERATURE RANGE |

| LTC3300ILXE-1#PBF | LTC3300ILXE-1#PBF  | LTC3300LXE-1  | 48-Lead (7mm × 7mm) Plastic eLQFP | -40°C to 125°C    |

| LTC3300HLXE-1#PBF | LTC3300HLXE-1#PBF  | LTC3300LXE-1  | 48-Lead (7mm × 7mm) Plastic eLQFP | -40°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 2) BOOST+ = 25.2V, C6 = 21.6V, C5 = 18V, C4 = 14.4V, C3 = 10.8V, C2 = 7.2V, C1 = 3.6V, V<sup>-</sup> = 0V, unless otherwise noted.

| SYMBOL                | PARAMETER                                                                   | CONDITIONS                                                                                                                                                                | MIN  | TYP                          | MAX                     | UNITS                      |

|-----------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|-------------------------|----------------------------|

| DC Specifica          | tions                                                                       |                                                                                                                                                                           |      |                              |                         |                            |

| $I_{Q\_SD}$           | Supply Current When Not<br>Balancing (Post Suspend or Pre<br>First Execute) | Measured at C1, C2, C3, C4, C5<br>Measured at C6<br>Measured at BOOST+                                                                                                    | 7    | 0<br>16<br>0                 | 1<br>25<br>10           | μΑ<br>μΑ<br>μΑ             |

| I <sub>Q_ACTIVE</sub> | Supply Current When Balancing (Note 3)                                      | Balancing C1 Only (Note 4 for V <sup>-</sup> , C2, C6) Measured at C1 Measured at C2, C3, C4, C5 Measured at C6 Measured at BOOST <sup>+</sup>                            |      | 250<br>70<br>560<br>0        | 375<br>105<br>840<br>10 | μΑ<br>μΑ<br>μΑ<br>μΑ       |

|                       |                                                                             | Balancing C2 Only (Note 4 for C1, C3, C6) Measured at C1 Measured at C2 Measured at C3, C4, C5 Measured at C6 Measured at BOOST+                                          | -105 | -70<br>250<br>70<br>560<br>0 | 375<br>105<br>840<br>10 | Ац<br>Ац<br>Ац<br>Ац       |

|                       |                                                                             | Balancing C3 Only (Note 4 for C2, C4, C6) Measured at C1, C4, C5 Measured at C2 Measured at C3 Measured at C6 Measured at BOOST+                                          | -105 | 70<br>-70<br>250<br>560<br>0 | 105<br>375<br>840<br>10 | Ац<br>Ац<br>Ац<br>Ац       |

|                       |                                                                             | Balancing C4 Only (Note 4 for C3, C5, C6) Measured at C1, C2, C5 Measured at C3 Measured at C4 Measured at C6 Measured at BOOST+                                          | -105 | 70<br>-70<br>250<br>560<br>0 | 105<br>375<br>840<br>10 | Ац<br>Ац<br>Ац<br>Ац<br>Ац |

|                       |                                                                             | Balancing C5 Only (Note 4 for C4, C6) Measured at C1, C2, C3 Measured at C4 Measured at C5 Measured at C6 Measured at BOOST+                                              | -105 | 70<br>-70<br>250<br>560<br>0 | 105<br>375<br>840<br>10 | Ац<br>Ац<br>Ац<br>Ац<br>Ац |

|                       |                                                                             | Balancing C6 Only (Note 4 for C5, C6, BOOST+) Measured at C1, C2, C3, C4 Measured at C5 Measured at C6 Measured at BOOST+ (BOOST = V-) Measured at BOOST+ (BOOST = V_REG) | -105 | 70<br>-70<br>740<br>60<br>0  | 105<br>1110<br>90<br>10 | Ац<br>Ац<br>Ац<br>Ац<br>Ац |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 2) BOOST+ = 25.2V, C6 = 21.6V, C5 = 18V, C4 = 14.4V, C3 = 10.8V, C2 = 7.2V, C1 = 3.6V, V<sup>-</sup> = 0V, unless otherwise noted.

| SYMBOL                      | PARAMETER                                                                           | CONDITIONS                                                                                                                                                                          |   | MIN                      | TYP              | MAX                      | UNITS       |

|-----------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------|------------------|--------------------------|-------------|

| I <sub>Q_EXTRA</sub>        | Supply Current Extra<br>(Serial I/O in Current Mode)                                | Additional Current Measured at C6, $V_{MODE} = V^-$ (CSBI Logic Low, SCKI and SDI Both Logic High; Refer to $I_{IL1}$ , $I_{IH1}$ , $I_{OH1}$ , $I_{OL1}$ Specs)                    |   |                          | 3.75             |                          | mA          |

| V <sub>CELL MIN</sub>       | Minimum Cell Voltage (Rising)<br>Required for Primary Gate Drive                    | Cn to $Cn-1$ Voltage to Balance $Cn$ , $n=2$ to 6<br>C1 Voltage to Balance C1<br>Cn+1 to $Cn$ Voltage to Balance $Cn$ , $n=1$ to 5<br>BOOST+ to C6 Voltage to Balance C6, BOOST = V | • | 1.8<br>1.8<br>1.8<br>1.8 | 2<br>2<br>2<br>2 | 2.2<br>2.2<br>2.2<br>2.2 | V<br>V<br>V |

| V <sub>CELL MIN(HYST)</sub> | V <sub>CELL MIN</sub> Comparator Hysteresis                                         |                                                                                                                                                                                     |   |                          | 70               |                          | mV          |

| V <sub>CELL MAX</sub>       | Maximum Cell Voltage (Rising)<br>Before Disabling Balancing                         | C1, $Cn$ to $Cn - 1$ Voltage to Balance Any Cell, $n = 2$ to 6                                                                                                                      | • | 4.7                      | 5                | 5.3                      | V           |

| V <sub>CELL MAX(HYST)</sub> | V <sub>CELL MAX</sub> Comparator Hysteresis                                         |                                                                                                                                                                                     |   |                          | 0.5              |                          | V           |

| V <sub>CELL RECONNECT</sub> | Maximum Cell Voltage (Falling) to Re-Enable Balancing                               |                                                                                                                                                                                     | • | 4.25                     |                  |                          | V           |

| V <sub>REG</sub>            | Regulator Pin Voltage                                                               | $9V \le C6 \le 36V$ , $0mA \le I_{L0AD} \le 20mA$                                                                                                                                   | • | 4.4                      | 4.8              | 5.2                      | V           |

| V <sub>REG POR</sub>        | V <sub>REG</sub> Voltage (Rising) for<br>Power-On Reset                             |                                                                                                                                                                                     |   |                          | 4.0              |                          | V           |

| V <sub>REG MIN</sub>        | Minimum V <sub>REG</sub> Voltage (Falling)<br>for Secondary Gate Drive              | $V_{REG}$ Voltage to Balance Cn, $n = 1$ to 6                                                                                                                                       | • | 3.8                      |                  |                          | V           |

| I <sub>REG_SC</sub>         | Regulator Pin Short Circuit Current<br>Limit                                        | V <sub>REG</sub> = 0V                                                                                                                                                               |   |                          | 55               |                          | mA          |

| V <sub>RTONP</sub>          | RTONP Servo Voltage                                                                 | $R_{RTONP} = 20k\Omega$                                                                                                                                                             | • | 1.158                    | 1.2              | 1.242                    | V           |

| V <sub>RTONS</sub>          | RTONS Servo Voltage                                                                 | $R_{RTONS} = 15k\Omega$                                                                                                                                                             | • | 1.158                    | 1.2              | 1.242                    | V           |

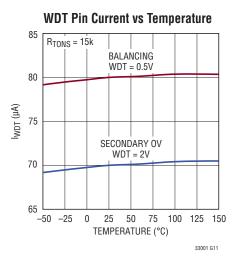

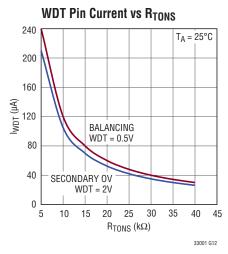

| I <sub>WDT_RISING</sub>     | WDT Pin Current, Balancing                                                          | $R_{TONS} = 15k\Omega$ , WDT = 0.5V                                                                                                                                                 | • | 72                       | 80               | 88                       | μА          |

| I <sub>WDT_FALLING</sub>    | WDT Pin Current as a Percentage of I <sub>WDT_RISING</sub> , Secondary OV           | $R_{TONS} = 15k\Omega$ , WDT = 2V                                                                                                                                                   | • | 85                       | 87.5             | 90                       | %           |

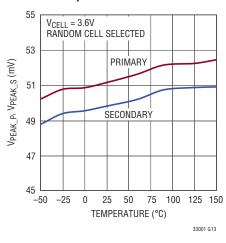

| V <sub>PEAK_P</sub>         | Primary Winding Peak Current<br>Sense Voltage                                       | I1P<br>I <i>n</i> P to C <i>n</i> – 1, <i>n</i> = 2 to 6                                                                                                                            | • | 45<br>45                 | 50<br>50         | 55<br>55                 | mV<br>mV    |

|                             | V <sub>PEAK_P</sub> Matching (All 6)                                                | ±[(Max – Min)/(Max + Min)] • 100%                                                                                                                                                   | • |                          | ±1.7             | ±5                       | %           |

| V <sub>PEAK_S</sub>         | Secondary Winding Peak Current<br>Sense Voltage                                     | InS to Cn – 1, n = 2 to 6, CTRL = 0 Only                                                                                                                                            | • | 45<br>45                 | 50<br>50         | 55<br>55                 | mV<br>mV    |

|                             | V <sub>PEAK_S</sub> Matching (All 6)                                                | ±[(Max – Min)/(Max + Min)] • 100%                                                                                                                                                   | • |                          | ±0.5             | ±3                       | %           |

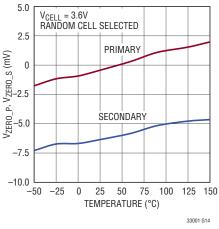

| V <sub>ZERO_P</sub>         | Primary Winding Zero Current<br>Sense Voltage (Note 5)                              | InP to Cn – 1, n = 2 to 6                                                                                                                                                           | • | −7<br>−7                 | -2<br>-2         | 3<br>3                   | mV<br>mV    |

|                             | V <sub>ZERO_P</sub> Matching (All 6)<br>Normalized to Mid-Range V <sub>PEAK_P</sub> | ±{[(Max – Min)/2]/(V <sub>PEAK_P MIDRANGE</sub> )} • 100%<br>(Note 6)                                                                                                               | • |                          | ±1.7             | ±5                       | %           |

| V <sub>ZERO_S</sub>         | Secondary Winding Zero Current<br>Sense Voltage (Note 5)                            | InS to Cn – 1, n = 2 to 6, CTRL = 0 Only                                                                                                                                            | • | −12<br>−12               | −7<br>−7         | -2<br>-2                 | mV<br>mV    |

|                             | V <sub>ZERO_S</sub> Matching (All 6)<br>Normalized to Mid-Range V <sub>PEAK_S</sub> | ±{[(Max – Min)/2]/(V <sub>PEAK_S MIDRANGE</sub> )} • 100% (Note 6)                                                                                                                  | • |                          | ±0.5             | ±3                       | %           |

| R <sub>BOOST_L</sub>        | BOOST <sup>-</sup> Pin Pull-Down R <sub>ON</sub>                                    | Measured at 100mA Into Pin, BOOST = V <sub>REG</sub>                                                                                                                                |   |                          | 2.5              |                          | Ω           |

| R <sub>BOOST_H</sub>        | BOOST <sup>-</sup> Pin Pull-Up R <sub>ON</sub>                                      | Measured at 100mA Out of Pin, BOOST = V <sub>REG</sub>                                                                                                                              |   |                          | 4                |                          | Ω           |

| T <sub>SD</sub>             | Thermal Shutdown Threshold (Note 7)                                                 | Rising Temperature                                                                                                                                                                  |   |                          | 155              |                          | °C          |

| T <sub>HYS</sub>            | Thermal Shutdown Hysteresis                                                         |                                                                                                                                                                                     |   |                          | 10               |                          | °C          |

| Timing Specifica            |                                                                                     |                                                                                                                                                                                     |   |                          |                  |                          |             |

| t <sub>r_P</sub>            | Primary Winding Gate Drive Rise<br>Time (10% to 90%)                                | G1P Through G6P, C <sub>GATE</sub> = 2500pF                                                                                                                                         |   |                          | 35               | 70                       | ns          |

| t <sub>f_P</sub>            | Primary Winding Gate Drive Fall<br>Time (90% to 10%)                                | G1P Through G6P, C <sub>GATE</sub> = 2500pF                                                                                                                                         |   |                          | 20               | 40                       | ns          |

LINEAR TECHNOLOGY

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . (Note 2) B00ST+ = 25.2V, C6 = 21.6V, C5 = 18V, C4 = 14.4V, C3 = 10.8V, C2 = 7.2V, C1 = 3.6V, V<sup>-</sup> = 0V, unless otherwise noted.

| SYMBOL                 | PARAMETER                                                                                         | CONDITIONS                                                                                                                        |       | MIN                                                            | TYP         | MAX               | UNITS          |

|------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------|-------------|-------------------|----------------|

| t <sub>r_S</sub>       | Secondary Winding Gate Drive                                                                      | G1S, C <sub>GATE</sub> = 2500pF                                                                                                   |       |                                                                | 30          | 60                | ns             |

|                        | Rise Time (10% to 90%)                                                                            | G2S Through G6S, CTRL = 0 Only, C <sub>GATE</sub> = 2500pF                                                                        |       |                                                                | 30          | 60                | ns             |

| t <sub>f_S</sub>       | Secondary Winding Gate Drive Fall<br>Time (90% to 10%)                                            | G1S, C <sub>GATE</sub> = 2500pF<br>G2S Through G6S, CTRL = 0 Only, C <sub>GATE</sub> = 2500pF                                     |       |                                                                | 20<br>20    | 40<br>40          | ns<br>ns       |

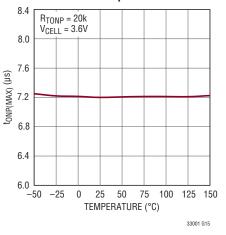

| t <sub>ONP MAX</sub>   | Primary Winding Switch Maximum On-Time                                                            | $R_{RTONP} = 20k\Omega$ (Measured at G1P-G6P)                                                                                     | •     | 6                                                              | 7.2         | 8.4               | μs             |

|                        | t <sub>ONPIMAX</sub> Matching (All 6)                                                             | ±[(Max - Min)/(Max + Min)] • 100%                                                                                                 | •     |                                                                | ±1          | ±4                | %              |

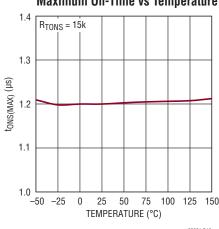

| tonsimax               | Secondary Winding Switch<br>Maximum On-Time                                                       | $R_{RTONS} = 15k\Omega$ (Measured at G1S-G6S)                                                                                     | •     | 1                                                              | 1.2         | 1.4               | μs             |

|                        | t <sub>ONSIMAX</sub> Matching (All 6)                                                             | ±[(Max – Min)/(Max + Min)] • 100%                                                                                                 | •     |                                                                | ±1          | ±4                | %              |

| t <sub>DLY_START</sub> | Delayed Start Time After New/<br>Different Balance Command or<br>Recovery from Voltage/Temp Fault |                                                                                                                                   |       |                                                                | 2           |                   | ms             |

| Voltage Mode           | e Timing Specifications                                                                           |                                                                                                                                   |       |                                                                |             |                   |                |

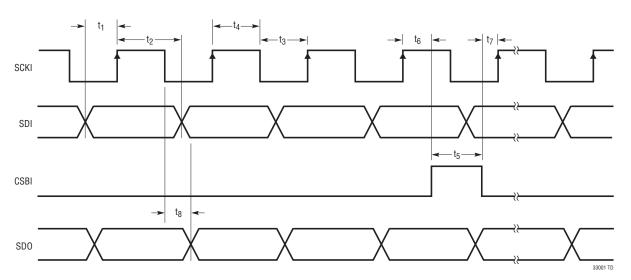

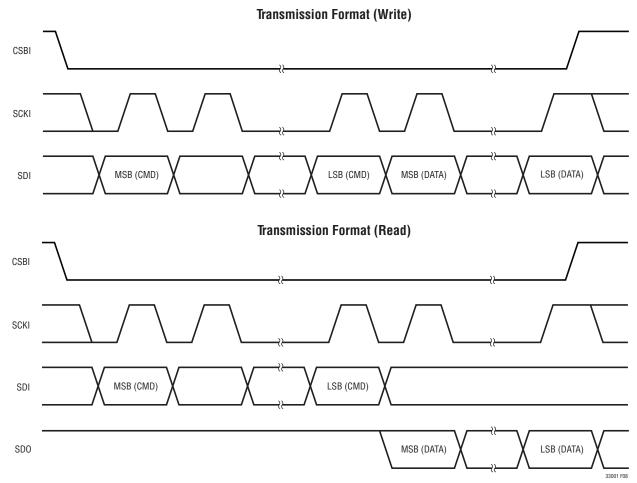

| t <sub>1</sub>         | SDI Valid to SCKI Rising Setup                                                                    | Write Operation                                                                                                                   | •     | 10                                                             |             |                   | ns             |

| t <sub>2</sub>         | SDI Valid from SCKI Rising Hold                                                                   | Write Operation                                                                                                                   | •     | 250                                                            |             |                   | ns             |

| t <sub>3</sub>         | SCKI Low                                                                                          |                                                                                                                                   | •     | 400                                                            |             |                   | ns             |

| t <sub>4</sub>         | SCKI High                                                                                         |                                                                                                                                   | •     | 400                                                            |             |                   | ns             |

| t <sub>5</sub>         | CSBI Pulse Width                                                                                  |                                                                                                                                   | •     | 400                                                            |             |                   | ns             |

| $t_6$                  | SCKI Rising to CSBI Rising                                                                        |                                                                                                                                   | •     | 100                                                            |             |                   | ns             |

| t <sub>7</sub>         | CSBI Falling to SCKI Rising                                                                       |                                                                                                                                   | •     | 100                                                            |             |                   | ns             |

| t <sub>8</sub>         | SCKI Falling to SDO Valid                                                                         | Read Operation                                                                                                                    | •     |                                                                |             | 250               | ns             |

| f <sub>CLK</sub>       | Clock Frequency                                                                                   |                                                                                                                                   | •     |                                                                |             | 1                 | MHz            |

| t <sub>WD1</sub>       | Watchdog Timer Timeout Period                                                                     | WDT Assertion Measured from Last Valid<br>Command Byte                                                                            | •     | 0.75                                                           | 1.5         | 2.25              | second         |

| t <sub>WD2</sub>       | Watchdog Timer Reset Time                                                                         | WDT Negation Measured from Last Valid<br>Command Byte                                                                             | •     |                                                                | 1.5         | 5                 | μs             |

| Current Mode           | e Timing Specifications                                                                           |                                                                                                                                   |       |                                                                |             |                   |                |

| t <sub>PD1</sub>       | CSBI to CSBO Delay                                                                                | C <sub>CSBO</sub> = 150pF                                                                                                         | •     |                                                                |             | 600               | ns             |

| t <sub>PD2</sub>       | SCKI Rising to SCKO Delay                                                                         | C <sub>SCKO</sub> = 150pF                                                                                                         | •     |                                                                |             | 300               | ns             |

| t <sub>PD3</sub>       | SDI to SDOI Delay                                                                                 | C <sub>SDOI</sub> = 150pF, Command Byte                                                                                           | •     |                                                                |             | 300               | ns             |

| t <sub>PD4</sub>       | SCKI Falling to SDOI Valid                                                                        | C <sub>SDOI</sub> = 150pF, Write Balance Command                                                                                  | •     |                                                                |             | 300               | ns             |

| t <sub>PD5</sub>       | SCKI Falling to SDI Valid                                                                         | C <sub>SDI</sub> = 150pF, Read Operation                                                                                          | •     |                                                                |             | 300               | ns             |

| t <sub>SCKO</sub>      | SCKO Pulse Width                                                                                  | C <sub>SCKO</sub> = 150pF                                                                                                         |       |                                                                | 100         |                   | ns             |

| Voltage Mode           | e Digital I/O Specifications                                                                      |                                                                                                                                   |       |                                                                |             |                   |                |

| V <sub>IH</sub>        | Digital Input Voltage High                                                                        | Pins CSBI, SCKI, SDI; V <sub>MODE</sub> = V <sub>REG</sub><br>Pins CTRL, BOOST, V <sub>MODE</sub> , TOS<br>Pin WDT                | • • • | $\begin{array}{c} V_{REG}-0.5 \\ V_{REG}-0.5 \\ 2 \end{array}$ |             |                   | V<br>V<br>V    |

| $V_{IL}$               | Digital Input Voltage Low                                                                         | Pins CSBI, SCKI, SDI; V <sub>MODE</sub> = V <sub>REG</sub><br>Pins CTRL, BOOST, V <sub>MODE</sub> , TOS<br>Pin WDT                | • • • |                                                                |             | 0.5<br>0.5<br>0.8 | V<br>V<br>V    |

| I <sub>IH</sub>        | Digital Input Current High                                                                        | Pins CSBI, SCKI, SDI; V <sub>MODE</sub> = V <sub>REG</sub><br>Pins CTRL, BOOST, V <sub>MODE</sub> , TOS<br>Pin WDT, Timed Out     |       | -1<br>-1<br>-1                                                 | 0<br>0<br>0 | 1<br>1<br>1       | μΑ<br>μΑ<br>μΑ |

| I <sub>IL</sub>        | Digital Input Current Low                                                                         | Pins CSBI, SCKI, SDI; V <sub>MODE</sub> = V <sub>REG</sub><br>Pins CTRL, BOOST, V <sub>MODE</sub> , TOS<br>Pin WDT, Not Balancing |       | -1<br>-1<br>-1                                                 | 0<br>0<br>0 | 1<br>1<br>1       | μΑ<br>μΑ<br>μΑ |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 2) BOOST<sup>+</sup> = 25.2V, C6 = 21.6V, C5 = 18V, C4 = 14.4V, C3 = 10.8V, C2 = 7.2V, C1 = 3.6V, V<sup>-</sup> = 0V, unless otherwise noted.

| SYMBOL           | PARAMETER                    | CONDITIONS                                                                                                                                                                                   |   | MIN                          | TYP                            | MAX                         | UNITS                |

|------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------|--------------------------------|-----------------------------|----------------------|

| $V_{0L}$         | Digital Output Voltage Low   | Pin SDO, Sinking 500μA; V <sub>MODE</sub> = V <sub>REG</sub> ; Read                                                                                                                          | • |                              |                                | 0.3                         | V                    |

| I <sub>OH</sub>  | Digital Output Current High  | Pin SDO at 6V                                                                                                                                                                                | • |                              |                                | 100                         | nA                   |

| Current Mode     | e Digital I/O Specifications |                                                                                                                                                                                              | · |                              |                                |                             |                      |

| I <sub>IL1</sub> | Digital Input Current Low    | Pin CSBI; V <sub>MODE</sub> = V <sup>-</sup><br>Pin SCKI; V <sub>MODE</sub> = V <sup>-</sup><br>Pin SDI, V <sub>MODE</sub> = V <sup>-</sup> , Write<br>Pin SDOI, TOS = V <sup>-</sup> , Read | • | -1500<br>-5<br>-5<br>0       | -1250<br>-2.5<br>-2.5<br>2.5   | -1000<br>0<br>0<br>5        | ДД<br>ДД<br>ДД<br>ДД |

| I <sub>IH1</sub> | Digital Input Current High   | Pin CSBI; V <sub>MODE</sub> = V <sup>-</sup><br>Pin SCKI; V <sub>MODE</sub> = V <sup>-</sup><br>Pin SDI, V <sub>MODE</sub> = V <sup>-</sup> , Write<br>Pin SDOI, TOS = V <sup>-</sup> , Read | • | -5<br>-1500<br>-1500<br>1000 | -2.5<br>-1250<br>-1250<br>1250 | 0<br>-1000<br>-1000<br>1500 | μΑ<br>μΑ<br>μΑ       |

| I <sub>OH1</sub> | Digital Output Current High  | Pin CSBO; TOS = V <sup>-</sup> Pin SCKO; TOS = V <sup>-</sup> Pin SDOI, TOS = V <sup>-</sup> , Write Pin SDI, V <sub>MODE</sub> = V <sup>-</sup> , Read                                      | • | 0<br>1000<br>1000            | 2.5<br>1250<br>1250            | 5<br>-1000                  | μΑ<br>μΑ<br>μΑ       |

| I <sub>OL1</sub> | Digital Output Current Low   | Pin CSBO; TOS = V <sup>-</sup> Pin SCKO; TOS = V <sup>-</sup> Pin SDOI, TOS = V <sup>-</sup> , Write Pin SDI, V <sub>MODE</sub> = V <sup>-</sup> , Read                                      | • | 1000<br>0<br>0<br>-5         | 1250<br>2.5<br>2.5             | 5<br>5                      | μΑ<br>μΑ<br>μΑ<br>μΑ |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3300-1 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3300I-1 is guaranteed over the  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  operating junction temperature range and the LTC3300H-1 is guaranteed over the  $-40^{\circ}\text{C}$  to  $150^{\circ}\text{C}$  operating junction temperature. High junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than  $125^{\circ}\text{C}$ . Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors. The junction temperature ( $T_J$ , in  ${}^{\circ}\text{C}$ ) is calculated from the ambient temperature ( $T_A$ , in  ${}^{\circ}\text{C}$ ) and power dissipation ( $P_D$ , in Watts) according to the formula:

$$T_J = T_A + (P_D \bullet \theta_{JA})$$

where  $\theta_{JA}$  (in °C/W) is the package thermal impedance.

**Note 3:** When balancing more than one cell at a time, the individual cell supply currents can be calculated from the values given in the table as follows: First add the appropriate table entries cell by cell for the balancers that are on. Second, *for each additional balancer that is on*, subtract  $70\mu A$  from the resultant sums for C1, C2, C3, C4, and C5, and  $450\mu A$  from the resultant sum for C6. For example, if all six balancers are on, the resultant current for C1 is  $[250-70+70+70+70+70-5(70)]\mu A=110\mu A$  and for C6 is  $[560+560+560+560+560+740-5(450)]\mu A=1290\mu A$ .

**Note 4:** Dynamic supply current is higher due to gate charge being delivered at the switching frequency during active balancing. See Gate Drivers/Gate Drive Comparators and Voltage Regulator in the Operation section for more information on estimating these currents.

**Note 5:** The zero current sense voltages given in the table are DC thresholds. The actual zero current sense voltage seen in application will be closer to zero due to the slew rate of the winding current and the finite delay of the current sense comparator.

**Note 6:** The mid-range value is the average of the minimum and maximum readings within the group of six.

**Note 7:** This IC includes overtemperature protection intended to protect the device during momentary overload conditions. The maximum junction temperature may be exceeded when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may result in device degradation or failure.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C unless otherwise specified.

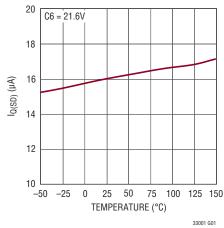

# C6 Supply Current When Not Balancing vs Temperature

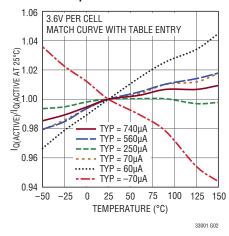

# Supply Current When Balancing vs Temperature Normalized to 25°C

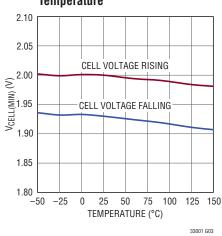

#### Minimum Cell Voltage Required for Primary Gate Drive vs Temperature

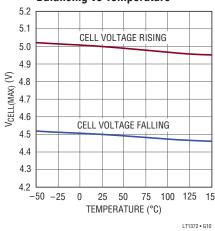

# Maximum Cell Voltage to Allow Balancing vs Temperature

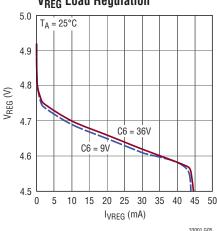

### **V<sub>REG</sub>** Load Regulation

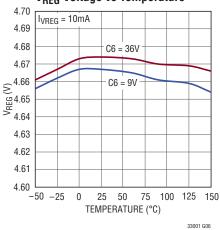

V<sub>REG</sub> Voltage vs Temperature

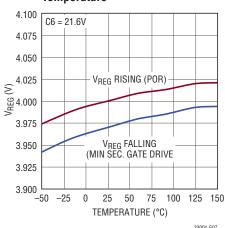

#### V<sub>REG</sub> POR Voltage and Minimum Secondary Gate Drive vs Temperature

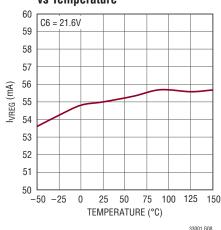

V<sub>REG</sub> Short-Circuit Current Limit vs Temperature

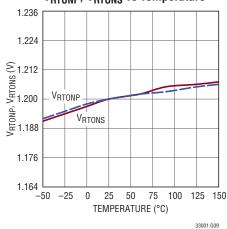

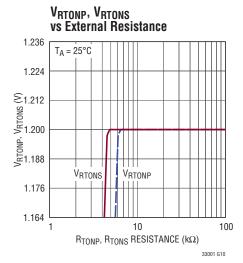

V<sub>RTONP</sub>, V<sub>RTONS</sub> vs Temperature

# TYPICAL PERFORMANCE CHARACTERISTICS TA = 25°C unless otherwise specified.

# Peak Current Sense Threshold vs Temperature

Primary Winding Switch Maximum On-Time vs Temperature

Secondary Winding Switch Maximum On-Time vs Temperature

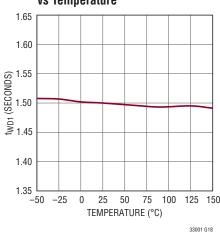

# Watchdog Timer Timeout Period vs Temperature

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ unless otherwise specified.

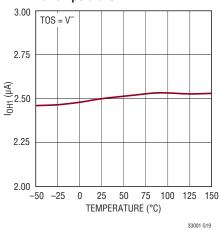

# CSBO Digital Output Current High vs Temperature

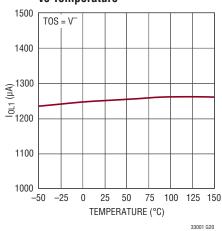

# CSBO Digital Output Current Low vs Temperature

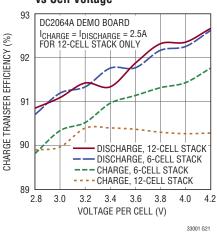

Balancer Efficiency vs Cell Voltage

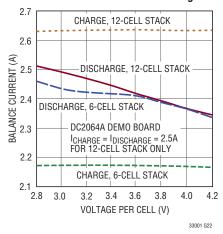

#### **Balance Current vs Cell Voltage**

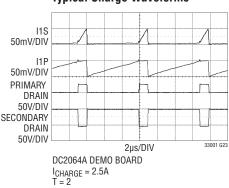

#### Typical Charge Waveforms

S = 12

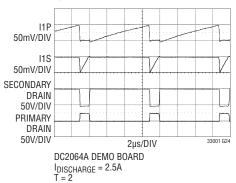

#### **Typical Discharge Waveforms**

S = 12

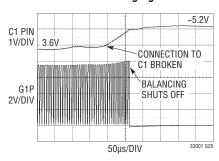

# Protection for Broken Connection to Cell While Charging

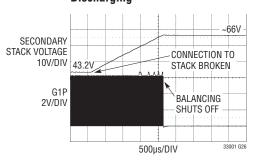

#### Protection for Broken Connection to Secondary Stack While Discharging

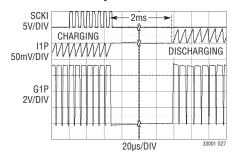

#### Changing Balancer Direction "On the Fly"

LINEAR

# PIN FUNCTIONS

Note: The convention adopted in this data sheet is to refer to the transformer winding paralleling an individual battery cell as the primary and the transformer winding paralleling multiple series-stacked cells as the secondary, *regardless* of the direction of energy transfer.

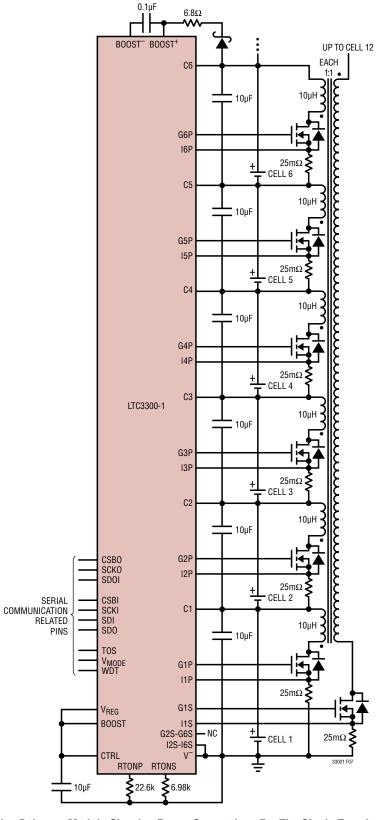

**G6S**, **G5S**, **G4S**, **G3S**, **G2S**, **G1S** (Pins 1, 3, 5, 7, 9, 11): G1S through G6S are gate driver outputs for driving external NMOS transistors connected in series with the secondary windings of transformers whose primaries are connected in parallel with battery cells 1 through 6. For the minimum part count balancing application employing a single transformer (CTRL =  $V_{REG}$ ), G2S through G6S are no connects.

**16S**, **15S**, **14S**, **13S**, **12S**, **11S** (**Pins 2**, **4**, **6**, **8**, **10**, **12**): I1S through I6S are current sense inputs for measuring secondary winding current in transformers whose primaries are connected in parallel with battery cells 1 through 6. For the minimum part count balancing application employing a single transformer (CTRL =  $V_{REG}$ ), I2S through I6S should be tied to  $V^-$ .

**RTONS (Pin 13):** Secondary Winding Max  $t_{ON}$  Setting Resistor. The RTONS pin servos to 1.2V. A resistor to V<sup>-</sup> programs the maximum on-time for all external NMOS transistors connected in series with secondary windings. This protects against a short-circuited current sense resistor in any secondary winding. To defeat this function, connect RTONS to  $V_{REG}$ . The secondary winding OVP threshold (see WDT pin) is also slaved to the value of the R<sub>TONS</sub> resistor.

**RTONP (Pin 14):** Primary Winding Max  $t_{ON}$  Setting Resistor. The RTONP pin servos to 1.2V. A resistor to V<sup>-</sup> programs the maximum on-time for all external NMOS transistors connected in series with primary windings. This protects against a short-circuited current sense resistor in any primary winding. To defeat this function, connect RTONP to  $V_{REG}$ .

**CTRL:** (Pin 15): Control Input. The CTRL pin configures the LTC3300-1 for the minimum part count application employing a single transformer if CTRL is tied to  $V_{REG}$  or for the multiple transformer application if CTRL is tied to  $V^-$ . This pin must be tied to either  $V_{REG}$  or  $V^-$ .

**CSBI** (**Pin 16**): Chip Select (Active Low) Input. The CSBI pin interfaces to a rail-to-rail output logic gate if  $V_{MODE}$  is tied to  $V_{REG}$ . CSBI must be driven by the CSBO pin of another LTC3300-1 if  $V_{MODE}$  is tied to  $V^-$ . See Serial Port in the Applications Information section.

**SCKI (Pin 17):** Serial Clock Input. The SCKI pin interfaces to a rail-to-rail output logic gate if  $V_{MODE}$  is tied to  $V_{REG}$ . SCKI must be driven by the SCKO pin of another LTC3300-1 if  $V_{MODE}$  is tied to  $V^-$ . See Serial Port in the Applications Information section.

**SDI (Pin 18):** Serial Data Input. When writing data to the LTC3300-1, the SDI pin interfaces to a rail-to-rail output logic gate if  $V_{MODE}$  is tied to  $V_{REG}$  or must be driven by the SDOI pin of another LTC3300-1 if  $V_{MODE}$  is tied to  $V^-$ . See Serial Port in the Applications Information section.

**SDO** (Pin 19): Serial Data Output. When reading data from the LTC3300-1, the SDO pin is an NMOS open-drain output if  $V_{MODE}$  is tied to  $V_{REG}$ . The SDO pin is not used if  $V_{MODE}$  is tied to  $V^-$ . See Serial Port in the Applications Information section.

**WDT (Pin 20):** Watchdog Timer Output (Active High). At initial power-up and when not attempting to execute a valid balance command, the WDT pin is high impedance and will be pulled high (internally clamped to  $\sim 5.6$ V) if an external pull-up resistor is present. While balancing (or attempting to balance but not able to due to voltage/temperature faults) and during normal communication activity, the WDT pin is pulled low by a precision current source slaved to the R<sub>TONS</sub> resistor. However, if no valid command byte is written for 1.5 seconds (typical), the WDT output will go back high. When WDT is high, all balancers are off. The watchdog timer function can be disabled by connecting WDT to V $^-$ . The secondary winding OVP function can also be implemented using this pin (See Operation section).

**V**<sup>-</sup> (**Pin 21**): Connect V<sup>-</sup> to the most negative potential in the series of cells.

**11P**, **12P**, **13P**, **14P**, **15P**, **16P** (**Pins 22**, **25**, **28**, **31**, **34**, **37**): 11P through 16P are current sense inputs for measuring primary winding current in transformers connected in parallel with battery cells 1 through 6.

LINEAR TECHNOLOGY

# PIN FUNCTIONS

**G1P**, **G2P**, **G3P**, **G4P**, **G5P**, **G6P** (**Pins 23**, **26**, **29**, **32**, **35**, **38**): G1P through G6P are gate driver outputs for driving external NMOS transistors connected in series with the primary windings of transformers connected in parallel with battery cells 1 through 6.

C1, C2, C3, C4, C5, C6 (Pins 24, 27, 30, 33, 36, 39): C1 through C6 connect to the positive terminals of battery cells 1 through 6. Connect the negative terminal of battery cell 1 to  $V^-$ .

**BOOST+** (**Pin 40**): Boost+ Pin. Connects to the anode of the external flying capacitor used for generating sufficient gate drive necessary for balancing the topmost battery cell in a given LTC3300-1 sub-stack. A Schottky diode from C6 to BOOST+ is needed as well. Alternately, the BOOST+ pin can connect to one cell up in the above sub-stack (if present). This pin is effectively C7. (Note: "Sub-stack" refers to the 3-6 battery cells connected locally to an individual LTC3300-1 as part of a larger stack.)

**BOOST**<sup>-</sup> (**Pin 41**): Boost<sup>-</sup> Pin. Connects to the cathode of the external flying capacitor used for generating sufficient gate drive necessary for balancing the topmost battery cell in a given LTC3300-1 sub-stack. Alternately, if the BOOST<sup>+</sup> pin connects to the next higher cell in the above sub-stack (if present), this pin is a no connect.

**BOOST (Pin 42):** Enable Boost Pin. Connect BOOST to  $V_{REG}$  to enable the boosted gate drive needed for balancing the top cell in a given LTC3300-1 sub-stack. If the BOOST+ pin can be connected to the next cell up in the stack (i.e., C1 of the next LTC3300-1 in the stack), then BOOST should be tied to  $V^-$  and BOOST- no connected. This pin must be tied to either  $V_{REG}$  or  $V^-$ .

**SDOI (Pin 43):** Serial Data Output/Input. SDOI transfers data to and from the next IC higher in the daisy chain when writing and reading. See Serial Port in the Applications Information section.

**SCKO** (Pin 44): Serial Clock Output. SCKO is a buffered and one-shotted version of the serial clock input, SCKI, when CSBI is low. SCKO drives the next IC higher in the daisy chain. See Serial Port in the Applications Information section.

**CSBO** (**Pin 45**): Chip Select (Active Low) Output. CSBO is a buffered version of the chip select input, CSBI. CSBO drives the next IC higher in the daisy chain. See Serial Port in the Applications Information section.

$V_{MODE}$  (Pin 46): Voltage Mode Input. When  $V_{MODE}$  is tied to  $V_{REG}$ , the CSBI, SCKI, SDI and SDO pins are configured as voltage inputs and outputs. This means these pins accept  $V_{REG}$ -referred rail-to-rail logic levels. Connect  $V_{MODE}$  to  $V_{REG}$  when the LTC3300-1 is the bottom device in a daisy chain.

When  $V_{MODE}$  is tied to  $V^-$ , the CSBI, SCKI and SDI pins are configured as current inputs and outputs, and SDO is unused. Connect  $V_{MODE}$  to  $V^-$  when the LTC3300-1 is being driven by another LTC3300-1 lower in the daisy chain. This pin must be tied to either  $V_{REG}$  or  $V^-$ .

**TOS (Pin 47):** Top Of Stack Input. Tie TOS to  $V_{REG}$  when the LTC3300-1 is the top device in a daisy chain. Tie TOS to  $V^-$  when the LTC3300-1 is any other device in the daisy chain. When TOS is tied to  $V_{REG}$ , the LTC3300-1 ignores the SDOI input. When TOS is tied to  $V^-$ , the LTC3300-1 expects data to be passed to and from the SDOI pin. This pin must be tied to either  $V_{REG}$  or  $V^-$ .

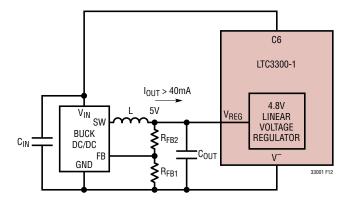

$V_{REG}$  (Pin 48): Linear Voltage Regulator Output. This 4.8V output should be bypassed with a 1µF or larger capacitor to V<sup>-</sup>. The  $V_{REG}$  pin is capable of supplying up to 40mA to internal and external loads. The  $V_{REG}$  pin does not sink current.

**V**<sup>-</sup> (Exposed Pad Pin 49): The exposed pad should be connected to a continuous (ground) plane biased at V<sup>-</sup> on the second layer of the printed circuit board by several vias directly under the LTC3300-1.

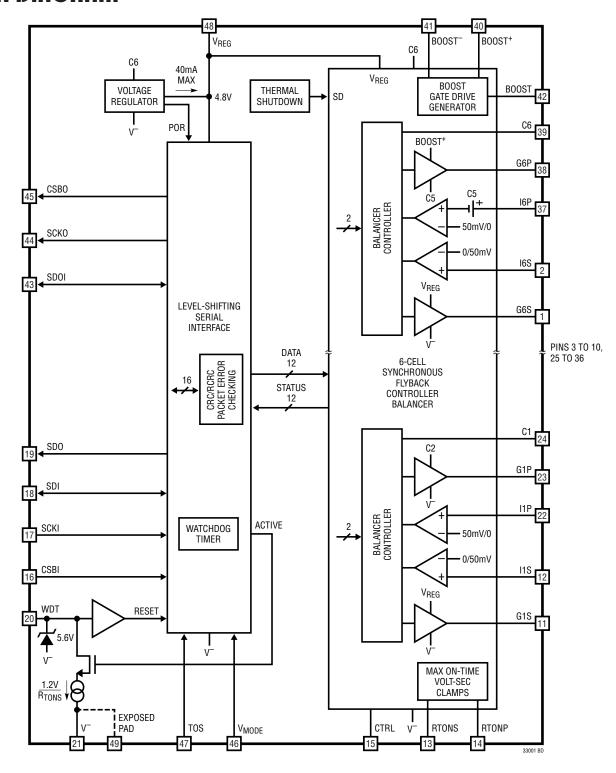

# **BLOCK DIAGRAM**

# TIMING DIAGRAM

# Timing Diagram of the Serial Interface

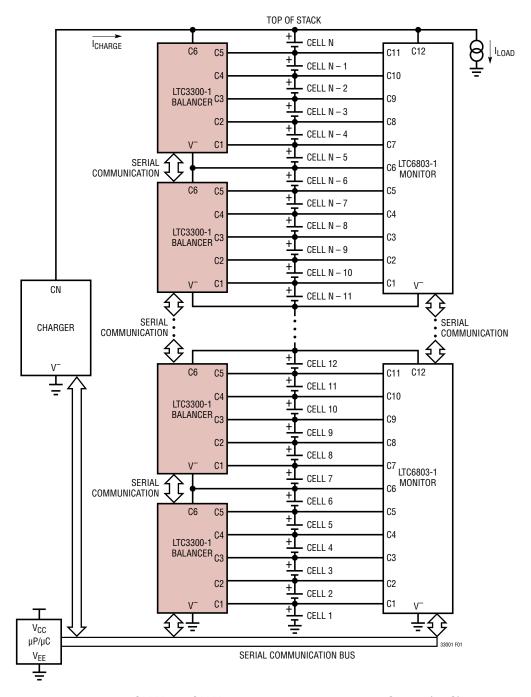

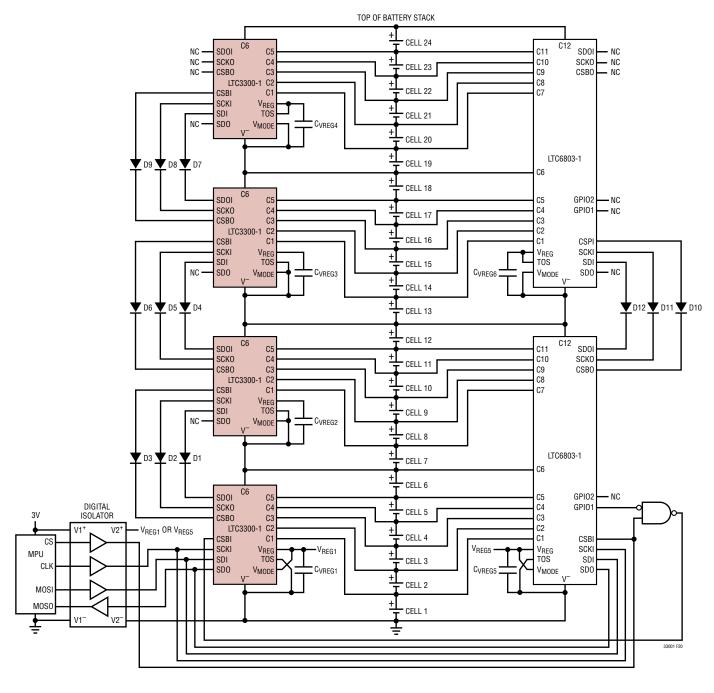

#### **Battery Management System (BMS)**

The LTC3300-1 multicell battery cell balancer is a key component in a high performance battery management system (BMS) for series-connected Li-lon cells. It is designed to operate in conjunction with a monitor, a charger, and a microprocessor or microcontroller (see Figure 1).

The function of the balancer is to efficiently transfer charge to/from a given out-of-balance cell in the stack from/to a larger group of neighboring cells (which includes that individual cell) in order to bring that cell into voltage or capacity balance with its neighboring cells. Ideally, this charge would always be transferred directly from/to the entire stack, but this is impractical for voltage reasons when the number of cells in the overall stack is large. The LTC3300-1 is designed to interface to a group of up to 6 series cells, so the number of LTC3300-1 ICs required to balance a series stack of N cells is N/6 rounded up to the nearest integer, with no limitation imposed on how large N can be. For connecting an individual LTC3300-1 in the stack to fewer than 6 cells, refer to the Applications Information section.

Because the balancing function entails switching large (multiampere) currents between cells, precision voltage monitoring in the BMS is better served by a dedicated monitor component such as the LTC6803-1 or one of its family of parts. The LTC6803-1 provides for high precision A/D monitoring of up to 12 series cells. The only voltage monitoring provided by the LTC3300-1 is a coarse "out-of-range" overvoltage and undervoltage cell balancing disqualification, which provides a safety shutoff in the event Kelvin sensing to the monitor component is lost.

In the process of bringing the cells into balance, the overall stack is slightly discharged. The charger component provides a means for net charging of the entire stack from an alternate power source.

The last component in the BMS is a microprocessor/microcontroller which communicates directly with the balancer, monitor, and charger to receive voltage, current, and temperature information and to implement a balancing algorithm.

There is no single balancing algorithm optimal for all situations. For example, during net charging of the overall stack, it may be desirable to discharge the highest voltage cells first to avoid reaching terminal charge on any cell before the entire stack is fully charged. Similarly, during net discharging of the overall stack, it may be desirable to charge the lowest voltage cells first to keep them from reaching a critically low level. Other algorithms may prioritize fastest time to overall balance. The LTC3300-1 implements no algorithm for balancing the stack. Instead it provides maximum flexibility by imposing no limitation on the algorithm implemented as all individual cell balancers can operate simultaneously and bidirectionally.

# **Unidirectional Versus Bidirectional Balancing**

Most balancers in use today employ a unidirectional (discharge only) approach. The simplest of these operate by switching in a resistor across the highest voltage cell(s) in the stack (passive balancing). No charge is recovered in this approach -instead it is dissipated as heat in the resistive element. This can be improved by employing an energy storage element (inductive or capacitive) to transfer

Figure 1. LTC3300-1/LTC6803-1 Typical Battery Management System (BMS)

charge from the highest voltage cell(s) in the stack to other lower voltage cells in the stack (active balancing). This can be very efficient (in terms of charge recovery) for the case where only a few cells in the overall stack are high, but will be very inefficient (and time consuming) for the case where only a few cells in the overall stack are low. A bidirectional active balancing approach, such as employed by the LTC3300-1, is needed to achieve minimum balancing time and maximum charge recovery for all common cell capacity errors.

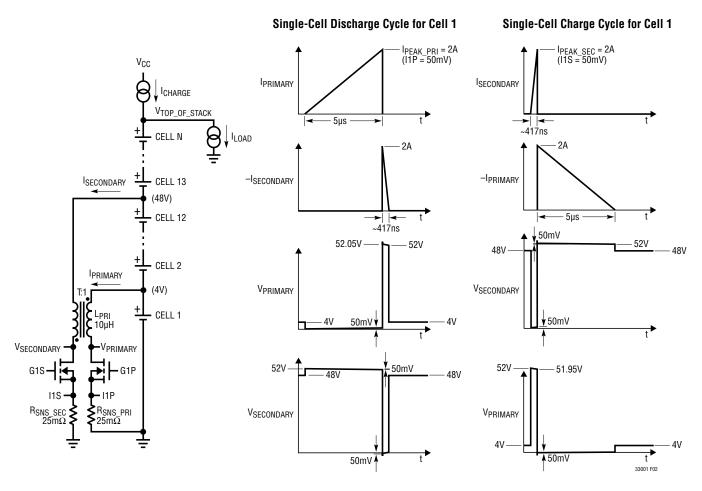

#### Synchronous Flyback Balancer

The balancing architecture implemented by the LTC3300-1 is bidirectional synchronous flyback. Each LTC3300-1 contains six independent synchronous flyback controllers that are capable of directly charging or discharging an individual cell. Balance current is scalable with external components. Each balancer operates independently of the others and provides a means for bidirectional charge transfer between an individual cell and a larger group of adjacent cells. Refer to Figure 2.

Figure 2. Synchronous Flyback Balancing Example with T = 1, S = 12

LINEAR

#### **Cell Discharging (Synchronous)**

When discharging is enabled for a given cell, the primary side switch is turned on and current ramps in the primary winding of the transformer until the programmed peak current ( $I_{PFAK-PRI}$ ) is detected at the  $I_nP$  pin. The primary side switch is then turned off, and the stored energy in the transformer is transferred to the secondary-side cells causing current to flow in the secondary winding of the transformer. The secondary-side synchronous switch is turned on to minimize power loss during the transfer period until the secondary current drops to zero (detected at InS). Once the secondary current reaches zero, the secondary switch turns off and the primary-side switch is turned back on thus repeating the cycle. In this manner, charge is transferred from the cell being discharged to all of the cells connected between the top and bottom of the secondary side—thereby charging the adjacent cells. In the example of Figure 2, the secondary-side connects across 12 cells including the cell being discharged.

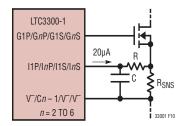

I<sub>PEAK PRI</sub> is programmed using the following equation:

$$I_{PEAK\_PRI} = \frac{50mV}{R_{SNS\_PRI}}$$

Cell discharge current (primary side) and secondary-side charge recovery current are determined to first order by the following equations:

$$I_{DISCHARGE} = \frac{I_{PEAK\_PRI}}{2} \left( \frac{S}{S+T} \right)$$

$$I_{SECONDARY} = \frac{I_{PEAK\_PRI}}{2} \left(\frac{1}{S+T}\right) \eta_{DISCHARGE}$$

where S is the number of secondary-side cells, 1:T is the transformer turns ratio from primary to secondary, and  $\eta_{DISCHARGE}$  is the transfer efficiency from primary cell discharge to the secondary side stack.

### **Cell Charging**

When charging is enabled for a given cell, the secondary-side switch for the enabled cell is turned on and current flows from the secondary-side cells through the transformer. Once  $I_{PEAK}$  SFC is reached in the secondary side

(detected at the InS pin), the secondary switch is turned off and current then flows in the primary side thus charging the selected cell from the entire stack of secondary cells. As with the discharging case, the primary-side synchronous switch is turned on to minimize power loss during the cell charging phase. Once the primary current drops to zero, the primary switch is turned off and the secondary-side switch is turned back on thus repeating the cycle.

I<sub>PEAK</sub> SEC is programmed using the following equation:

$$I_{PEAK\_SEC} = \frac{50mV}{R_{SNS\_SEC}}$$

Cell charge current and corresponding secondary-side discharge current are determined to first order by the following equations:

$$I_{CHARGE} = \frac{I_{PEAK\_SEC}}{2} \left( \frac{ST}{S+T} \right) \eta_{CHARGE}$$

$$I_{SECONDARY} = \frac{I_{PEAK\_SEC}}{2} \left( \frac{T}{S+T} \right)$$

where S is the number of secondary cells in the stack, 1:T is the transformer turns ratio from primary to secondary, and  $\eta_{CHARGE}$  is the transfer efficiency from secondary-side stack discharge to the primary-side cell.

Each balancer's charge transfer "frequency" and duty factor depend on a number of factors including  $I_{PEAK\_PRI}$ ,  $I_{PEAK\_SEC}$ , transformer winding inductances, turns ratio, cell voltage and the number of secondary-side cells.

The frequency of switching seen at the gate driver outputs is given by:

$$f_{DISCHARGE} = \frac{S}{S+T} \bullet \frac{V_{CELL}}{L_{PRI} \bullet I_{PEAK\_PRI}}$$

$$f_{CHARGE} = \frac{S}{S+T} \bullet \frac{V_{CELL}}{L_{PRI} \bullet I_{PEAK} \quad SEC} \bullet T$$

where  $L_{\text{PRI}}$  is the primary winding inductance.

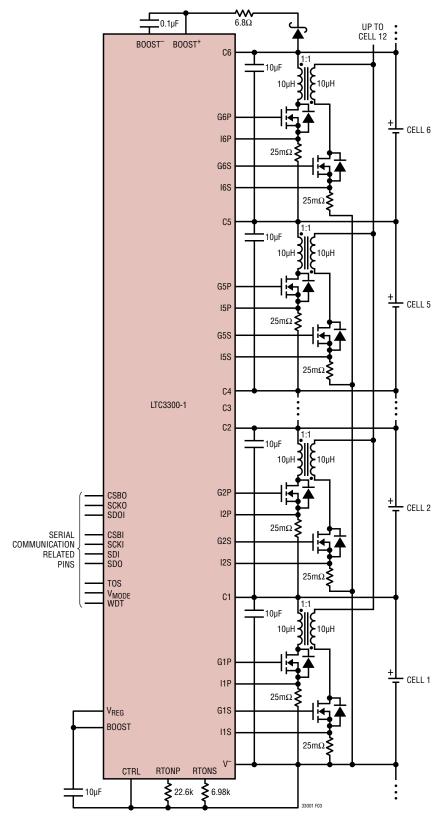

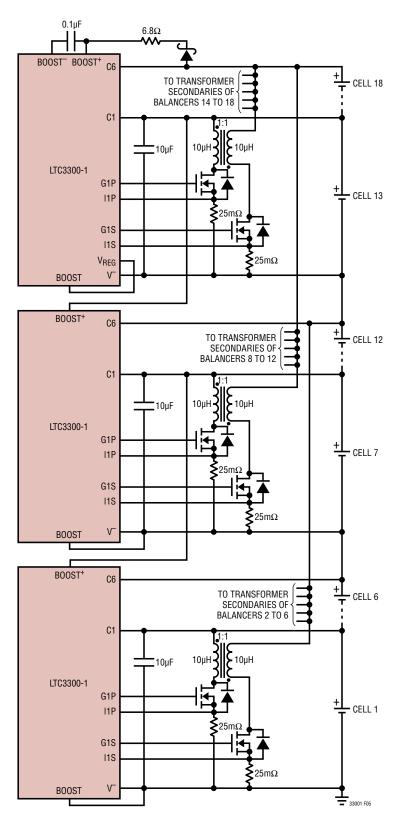

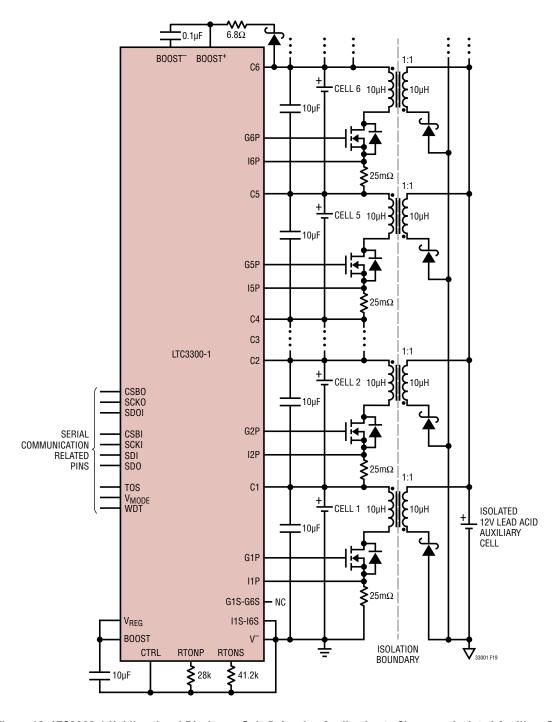

Figure 3 shows a fully populated LTC3300-1 application employing all six balancers.

Figure 3. LTC3300-1 6-Cell Active Balancer Module Showing Power Connections for the Multi-Transformer Application (CTRL = V<sup>-</sup>)

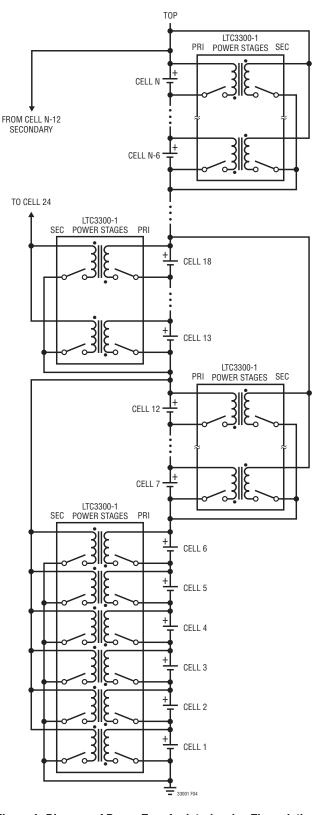

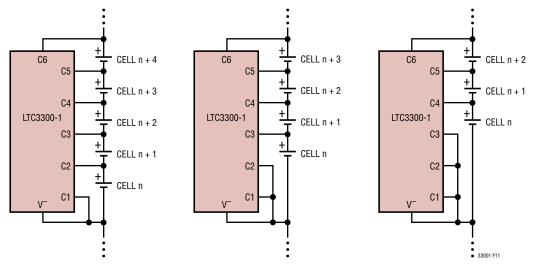

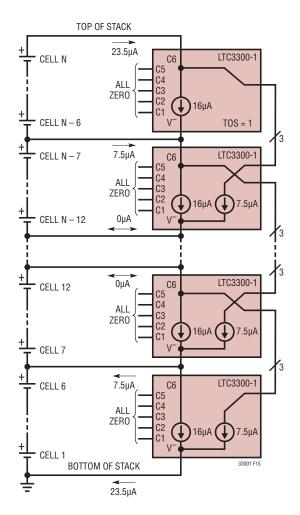

#### **Balancing High Voltage Battery Stacks**

Balancing series connected batteries which contain >>12 cells in series requires interleaving of the transformer secondary connections in order to achieve full stack balancing while limiting the breakdown voltage requirements of the primary- and secondary-side power FETs. Figure 4 shows typical interleaved transformer connections for a multicell battery stack in the generic sense, and Figure 5 for the specific case of an 18-cell stack. In these examples, the secondary side of each transformer is connected to the top of the cell that is 12 positions higher in the stack than the bottom of the lowest voltage cell in each LTC3300-1 sub-stack. For the top most LTC3300-1 in the stack, it is not possible to connect the secondary side of the transformer across 12 cells. Instead, it is connected to the top of the stack, or effectively across only 6 cells. Interleaving in this fashion allows charge to transfer between 6-cell sub-stacks throughout the entire battery stack.

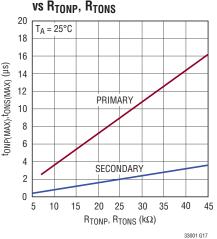

#### Max On-Time Volt-Sec Clamps

The LTC3300-1 contains programmable fault protection clamps which limit the amount of time that current is allowed to ramp in either the primary or secondary windings in the event of a shorted sense resistor. Maximum on time for all primary connections (active during cell discharging) and all secondary connections (active during cell charging) is individually programmable by connecting resistors from the  $R_{\mbox{\scriptsize TONP}}$  and  $R_{\mbox{\scriptsize TONS}}$  pins to  $V^-$  according to the following equations:

$$t_{ON(MAX)|PRIMARY} = 7.2 \mu s \frac{R_{TONP}}{20 k\Omega}$$

$$t_{ON(MAX)|SECONDARY} = 1.2 \mu s \frac{R_{TONS}}{15 k\Omega}$$

For more information on selecting the appropriate maximum on-times, refer to the Applications Information section.

To defeat this function, short the appropriate  $R_{TON}$  pin(s) to  $V_{RFG}$ .

Figure 4. Diagram of Power Transfer Interleaving Through the Stack, Transformer Connections for High Voltage Stacks

Figure 5. 18-Cell Active Balancer Showing Power Connections, Interleaved Transformer Secondaries and BOOST\* Rail Generation Up the Stack

LINEAR

#### **Gate Drivers/Gate Drive Comparators**

All secondary-side gate drivers (G1S through G6S) are powered from the V<sub>REG</sub> output, pulling up to 4.8V when on and pulling down to V when off. All primary-side gate drivers (G1P through G6P) are powered from their respective cell voltage and the next cell voltage higher in the stack (see Table 1). An individual cell balancer will only be enabled if its corresponding cell voltage is greater than 2V and the cell voltage of the next higher cell in the stack is also greater than 2V. For the G6P gate driver output, the next higher cell in the stack is C1 of the next higher LTC3300-1 in the stack (if present) and is only used if the boosted gate drive is disabled (by connecting BOOST = V<sup>-</sup>). If the boosted gate drive is enabled (by connecting  $BOOST = V_{RFG}$ ), only the C6 cell voltage is looked at to enable balancing of Cell 6. In the case of the topmost LTC3300-1 in the stack, the boosted gate drive must be enabled. The boosted gate drive requires an external diode from C6 to BOOST<sup>+</sup> and a boost capacitor from BOOST<sup>+</sup> to BOOST<sup>-</sup>. For information on selecting these components. refer to the Applications Information section. Also note that the dynamic supply current referred to in Note 4 of the Electrical Characteristics table adds to the terminal currents of the pins indicated in the Voltage When Off and Voltage When On columns of Table 1.

The gate drive comparators have a DC hysteresis of 70mV. For improved noise immunity, the inputs are internally

low pass filtered and the outputs are filtered so as to not transition unless the internal comparator state is unchanged for 3µs to 6µs (typical). If insufficient gate drive is detected while active balancing is in progress (perhaps, for example, if the stack is under heavy load), the affected balancer(s) and only the affected balancer(s) will shut off. The balance command remains stored in memory, and active balancing will resume where it left off if sufficient gate drive is subsequently restored. This can happen if, for example, the stack is being charged.

#### **Cell Overvoltage Comparators**

In addition to sufficient gate drive being required to enable balancing, there are additional comparators which disable all active balancing if any of the six individual cell voltages is greater than 5V. These comparators have a DC hysteresis of 500mV. For improved noise immunity, the inputs are internally low pass filtered and the outputs are filtered so as to not transition unless the internal comparator state is unchanged for 3µs to 6µs (typical). If any cell voltage goes overvoltage while active balancing is in progress, all active balancers will shut off. The balance command remains stored in memory, and active balancing will resume where if left off if the cell voltage subsequently comes back in range. These comparators will protect the LTC3300-1 if a connection to a battery is lost while balancing and the cell voltage is still increasing as a result of that balancing.

Table 1

| DRIVER OUTPUT | VOLTAGE WHEN OFF | VOLTAGE WHEN ON                                  | GATE DRIVE REQUIRED TO ENABLE BALANCING          |

|---------------|------------------|--------------------------------------------------|--------------------------------------------------|

| G1P           | V-               | C2                                               | $(C2 - C1) \ge 2V$ and $(C1 - V^{-}) \ge 2V$     |

| G2P           | C1               | C3                                               | $(C3 - C2) \ge 2V$ and $(C2 - C1) \ge 2V$        |

| G3P           | C2               | C4                                               | $(C4 - C3) \ge 2V$ and $(C3 - C2) \ge 2V$        |

| G4P           | C3               | C5                                               | $(C5 - C4) \ge 2V$ and $(C4 - C3) \ge 2V$        |

| G5P           | C4               | C6                                               | $(C6 - C5) \ge 2V \text{ and } (C5 - C4) \ge 2V$ |

| G6P           | C5               | If BOOST = V <sub>REG</sub> : BOOST+ (Generated) | (C6 – C5) ≥ 2V                                   |

|               |                  | If BOOST = V <sup>-</sup> : BOOST+ = C7*         | $(C7^* - C6) \ge 2V$ and $(C6 - C5) \ge 2V$      |

<sup>\*</sup>C7 is equal to C1 of the next higher LTC3300-1 in the stack if this connection is used.

#### **Voltage Regulator**

A linear voltage regulator powered from C6 creates a 4.8V rail at the V<sub>REG</sub> pin which is used for powering certain internal circuitry of the LTC3300-1 including all 6 secondary gate drivers. The V<sub>RFG</sub> output can also be used for powering external loads, provided that the total DC loading of the regulator does not exceed 40mA at which point current limit is imposed to limit on-chip power dissipation. The internal component of the DC load current is dominated by the average gate driver current(s) (G1S through G6S), each approximated by C • V • f, where C is the gate capacitance of the external NMOS transistor,  $V = V_{RFG} = 4.8V$ , and f is the frequency that the gate driver output is running at. FET manufacturers usually specify the  $C \bullet V$  product as  $Q_q$  (gate charge) measured in coulombs at a given gate drive voltage. The frequency, f, is dependent on many terms, primarily the voltage of each individual cell, the number of cells in the secondary stack, the programmed peak balancing current, and the transformer primary and secondary winding inductances. In a typical application, the C • V • f current loading the V<sub>RFG</sub> output is expected to be low single-digit milliamperes per driver. Note that the V<sub>REG</sub> loading current is ultimately delivered from the C6 pin. For applications involving very large balance currents and/or employing external NMOS transistors with very large gate capacitance, the V<sub>RFG</sub> output may need to source more than 40mA average. For information on how to design for these situations, refer to the Applications Information section.

One additional function slaved to the  $V_{REG}$  output is the power-on reset (POR). During initial power-up and subsequently if the  $V_{REG}$  pin voltage ever falls below approximately 4V (e.g., due to overloading), the serial port is cleared to the default power-up state with no balancers active. This feature thus guarantees that the minimum gate drive provided to the external secondary side FETs is also 4V. For a  $10\mu F$  capacitor loading the output at initial power-up, the output reaches regulation in approximately 1ms.

#### Thermal Shutdown

The LTC3300-1 has an overtemperature protection circuit which shuts down all active balancing if the internal silicon die temperature rises to approximately 155°C. When in thermal shutdown, all serial communication remains active and the cell balancer status (which contains temperature information) can be read back. The balance command which had been being executed remains stored in memory. This function has 10°C of hysteresis so that when the die temperature subsequently falls to approximately 145°C, active balancing will resume with the previously executing command.

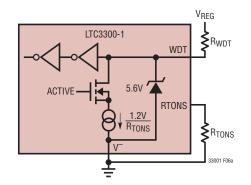

### **Watchdog Timer Circuit**

The watchdog timer circuit provides a means of shutting down all active balancing in the event that communication to the LTC3300-1 is lost. The watchdog timer initiates when a balance command begins executing and is reset to zero every time a valid 8-bit command byte (see Serial Port Operation) is written. The valid command byte can be an execute, a write, or a read (command or status). "Partial" reads and writes are considered valid, i.e., it is only necessary that the first 8 bits have to be written and contain the correct address.

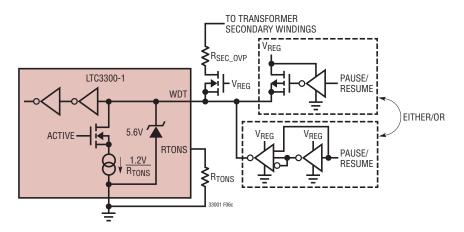

Referring to Figure 6a, at initial power-up and when not balancing, the WDT pin is high impedance and will be pulled high (internally clamped to ~5.6V) if an external pull-up resistor is present. While balancing and during normal communication activity, the WDT pin is pulled low by a precision current source equal to  $1.2V/R_{TONS}$ . (Note: if the secondary volt-second clamp is defeated by connecting  $R_{TONS}$  to  $V_{REG}$ , the watchdog function is also defeated.) If no valid command byte is written for 1.5 seconds (typical), the WDT output will go back high. When WDT is high, all balancers will be shut down but the previously executing balance command still remains in memory. From this timed-out state, a subsequent valid command byte will reset the timer, but the balancers will

only restart if an execute command is written. To defeat the watchdog function, simply connect the WDT pin to V<sup>-</sup>.

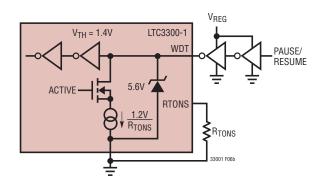

#### Pause/Resume Balancing (via WDT Pin)

The WDT output pin doubles as a logic input (TTL levels) which can be driven by an external logic gate as shown in Figure 6b (no watchdog), or by a PMOS/three-state logic gate as shown in Figure 6c (with watchdog) to pause and resume balancing in progress. The external pull-up must have sufficient drive capability to override the current source to ground at the WDT pin (=1.2V/R<sub>TONS</sub>). Provided that the internal watchdog timer has not independently timed

out, externally pulling the WDT pin high will immediately pause balancing, and it will resume where it left off when the pin is released.

### Secondary Winding OVP Function (via WDT pin)

The precision current source pull-down on the WDT pin during balancing can be used to construct an accurate secondary winding OVP protection circuit as shown in Figure 6c. A second external resistor, scaled to  $R_{TONS}$  and connected to the transformer secondary winding, is used to set the comparator threshold. An NMOS cascode device (with gate tied to  $V_{REG}$ ) is also needed to protect

(6a) Watchdog Timer Only (WDT = V- to Defeat)

(6b) Pause/Resume Balancing Only

(6c) Watchdog Timer with Pause/Resume Balancing and Secondary Winding OVP Protection

Figure 6. WDT Pin Connection Options

the WDT pin from high voltage. The secondary winding OVP thresholds are given by:

$V_{SEC|OVP(RISING)} = 1.4V + 1.2V \bullet (R_{SEC\_OVP}/R_{TONS})$

V<sub>SECIOVP(FALLING)</sub> = 1.4V + 1.05V • (R<sub>SEC OVP</sub>/R<sub>TONS</sub>)

This comparator will protect the LTC3300-1 application circuit if the secondary winding connection to the battery stack is lost while balancing and the secondary winding voltage is still increasing as a result of that balancing. The balance command remains stored in memory, and active balancing will resume where it left off if the stack voltage subsequently falls to a safer level.

### Single Transformer Application (CTRL = $V_{RFG}$ )

Figure 7 shows a fully populated LTC3300-1 application employing all six balancers with a single shared custom transformer. In this application, the transformer has six primary windings coupled to a single secondary winding. Only one balancer can be active at a given time as all six share the secondary gate driver G1S and secondary current sense input I1S. The unused gate driver outputs G2S-G6S must be left floating and the unused current sense inputs I2S-I6S should be connected to V<sup>-</sup>. Any balance command which attempts to operate more than one balancer at a time will be ignored. This application represents the minimum component count active balancer achievable.

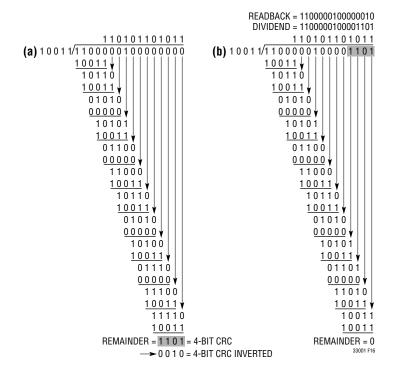

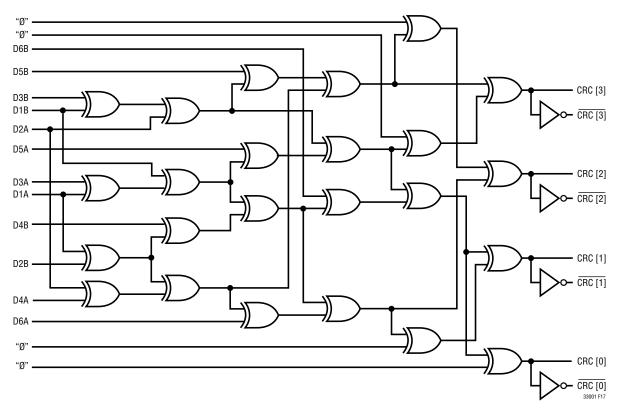

#### SERIAL PORT OPERATION

#### Overview

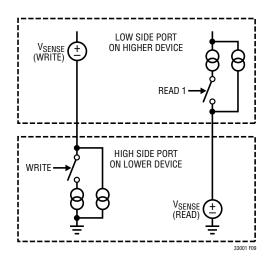

The LTC3300-1 has an SPI bus compatible serial port. Several devices can be daisy chained in series. There are two sets of serial port pins, designated as low side and high side. The low side and high side ports enable devices to be daisy chained even when they operate at different power supply potentials. In a typical configuration, the positive power supply of the first, bottom device is connected to the negative power supply of the second, top device. When devices are stacked in this manner, they can

be daisy chained by connecting the high side port of the bottom device to the low side port of the top device. With this arrangement, the master writes to or reads from the cascaded devices as if they formed one long shift register. The LTC3300-1 translates the voltage level of the signals between the low side and high side ports to pass data up and down the battery stack.

#### **Physical Layer**

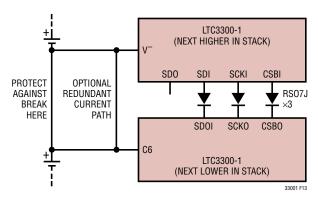

On the LTC3300-1, seven pins comprise the low side and high side ports. The low side pins are CSBI, SCKI, SDI and SDO. The high side pins are CSBO, SCKO and SDOI. CSBI and SCKI are always inputs, driven by the master or by the next lower device in a stack. CSBO and SCKO are always outputs that can drive the next higher device in a stack. SDI is a data input when writing to a stack of devices. For devices not at the bottom of a stack, SDI is a data output when reading from the stack. SDOI is a data output when writing to and a data input when reading from a stack of devices. SDO is an open-drain output that is only used on the bottom device of a stack, where it may be tied with SDI, if desired, to form a single, bidirectional port. The SDO pin on the bottom device of a stack requires a pull-up resistor. For devices up in the stack, SDO should be tied to the local V<sup>-</sup> or left floating.

To communicate between daisy-chained devices, the high side port pins of a lower device (CSBO, SCKO and SDOI) should be connected through high voltage diodes to the respective low side port pins of the next higher device (CSBI, SCKI and SDI). In this configuration, the devices communicate using current rather than voltage. To signal a logic high from the lower device to the higher device, the lower device sinks a smaller current from the higher device pin. To signal a logic low, the lower device sinks a larger current. Likewise, to signal a logic high from the higher device to the lower device, the higher device sources a larger current to the lower device pin. To signal a logic low, the higher device sources a smaller current.

Figure 7. LTC3300-1 6-Cell Active Balancer Module Showing Power Connections For The Single Transformer Application (CTRL = V<sub>REG</sub>)

33001fb

Figure 8

See Figure 9. Since CSBO, SCKO and SDOI voltages are close to the  $V^-$  of the high side device, the  $V^-$  of the high side device must be at least 5V higher than that of the low side device to guarantee current flows of the current mode interface. It is recommended that high voltage diodes be placed in series with the SPI daisy-chain signals as shown if Figure 13. These diodes prevent reverse voltage stress on the IC if a battery group bus bar is removed. See Battery Interconnection Integrity for additional information.

Standby current consumed in the current mode serial interface is minimized when CSBI is logic high.

The voltage mode pin  $(V_{MODE})$  determines whether the low side serial port is configured as voltage mode or current mode. For the bottom device in a daisy-chain stack, this

Figure 9. Current Mode Interface

LINEAR

pin must be pulled high (tied to  $V_{REG}$ ). The other devices in the daisy chain must have this pin pulled low (tied to  $V^-$ ) to designate current mode communication. To designate the top-of-stack device, the TOS pin on the top device of a daisy chain must be tied high. The other devices in the stack must have TOS tied low. See the application on the last page of this data sheet.

#### **Command Byte**