# EMC6D102

# Fan Control Device with Hardware Monitoring and Acoustic Noise Reduction Features

Datasheet

## PRODUCT FEATURES

- 3.3 Volt Operation (5 Volt Tolerant Input Buffers)

- SMBus 2.0 compliant interface (Fixed, Not Discoverable) With Three Slave Address Options

- Fan Control

- PWM (Pulse width Modulation) Outputs (3)

- Fan Tachometer Inputs (4)

- Individual status and enable bits per tach input

- Programmable automatic fan control based on temperature

- Fan ramp rate control for acoustic noise reduction

- Temperature Monitor

- Monitoring of Two Remote Thermal Diodes (+/- 3 deg C accuracy)

- Internal Ambient Temperature Measurement

- Limit Comparison of all Monitored Values

- Individual status and enable bits per thermal input

- Interrupt Pin for out-of-limit Temperature Indication

- Configurable offset for internal or external temperature channels.

- Supports 4 programmable temperature averaging modes

- 2 monitoring modes: Continuous or Cycle (Power Saving mode)

- Offers 2 Low Power Modes when monitoring is off: Sleep and Shutdown

## Voltage Monitor

- Monitor Power supplies (+2.5V, +5V, +12V, Vccp, and VCC)

- Individual status and enable bits per voltage input

- Limit Comparison of all Monitored Values

- Interrupt Pin for out-of-limit Voltage Indication

- Supports 4 programmable voltage averaging modes

- 2 monitoring modes: Continuous or Cycle (Power Saving mode)

- Offers 2 Low Power Modes when monitoring is off: Sleep and Shutdown

- 5 VID (Voltage Identification) inputs

- XOR Tree test mode

- 24-pin, SSOP Lead-Free RoHS Compliant package

## **ORDER NUMBERS:**

EMC6D102-CZC FOR 24 PIN SSOP LEAD-FREE ROHS COMPLIANT PACKAGE EMC6D102-CZC-TR FOR 24 PIN SSOP LEAD-FREE ROHS COMPLIANT PACKAGE

80 ARKAY DRIVE, HAUPPAUGE, NY 11788 (631) 435-6000, FAX (631) 273-3123

Copyright © 2007 SMSC or its subsidiaries. All rights reserved.

Circuit diagrams and other information relating to SMSC products are included as a means of illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been checked and is believed to be accurate, no responsibility is assumed for inaccuracies. SMSC reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your local SMSC sales office to obtain the latest specifications before placing your product order. The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights or other intellectual property rights of SMSC or others. All sales are expressly conditional on your agreement to the terms and conditions of the most recently dated version of SMSC's standard Terms of Sale Agreement dated before the date of your order (the "Terms of Sale Agreement"). The product may contain design defects or errors known as anomalies which may cause the product's functions to deviate from published specifications. Anomaly sheets are available upon request. SMSC products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of SMSC and further testing and/or modification will be fully at the risk of the customer. Copies of this document or other SMSC literature, as well as the Terms of Sale Agreement, may be obtained by visiting SMSC's website at http://www.smsc.com. SMSC is a registered trademark of Standard Microsystems Corporation ("SMSC"). Product names and company names are the trademarks of their respective holders.

SMSC DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE. IN NO EVENT SHALL SMSC BE LIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF SMSC OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER OR NOT SMSC HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

## **Table of Contents**

| Chap               | oter 1   | General Description                 | 8 |

|--------------------|----------|-------------------------------------|---|

| Chap               | oter 2   | Pinout                              | 9 |

| <b>Chap</b><br>3.1 |          | Pin Description                     |   |

| 3.2                |          | Type Description                    |   |

| 3.3                |          | peration, 5V Tolerance              |   |

| Chan               | oter 4   | SMBus Interface                     | 3 |

| 4.1                |          | \ddress                             |   |

| 4.2                |          | Bus Interface                       |   |

| 4.3                |          | otocols                             |   |

| 4.4                |          | Protocol Response Behavior          |   |

|                    | 4.4.1    | Undefined Registers                 | 5 |

| 4.5                | Genera   | I Call Address Response             | 5 |

| 4.6                | Slave D  | Device Time-Out.                    | 6 |

| 4.7                | Stretchi | ing the SCLK Signal                 | 6 |

| 4.8                | SMBus    | Timing 1                            | 6 |

| 4.9                | Bus Re   | set Sequence                        | 6 |

| 4.10               | SMBus    | Alert Response Address 1            | 6 |

| Chap               | oter 5   | Hardware Monitoring                 | 8 |

| 5.1                |          | onitoring                           |   |

| 5.2                |          | ng the EMC6D102                     |   |

| 0.2                | 5.2.1    | Power-On Reset                      |   |

|                    | 5.2.2    | Soft Reset (Initialization)         |   |

| 5.3                | -        | ing Modes                           |   |

| 0.0                | 5.3.1    | Continuous Monitoring Mode          |   |

|                    | 5.3.2    | Cycle Monitoring Mode               |   |

| 5.4                |          | of Status Registers                 |   |

| 0.1                | 5.4.1    | Diode Fault                         |   |

| 5.5                | -        | 2 bit Pin                           |   |

| 5.6                | •        | wer Modes                           |   |

| 0.0                | 5.6.1    | Sleep Mode                          |   |

|                    | 5.6.2    | Shutdown Mode                       |   |

| 5.7                |          | Voltage Measurement                 |   |

| 5.8                | -        | 2 ID                                |   |

| 5.9                |          | rature Measurement                  |   |

| 0.0                | 5.9.1    | Internal Temperature Measurement    |   |

|                    | 5.9.2    | External Temperature Measurement    |   |

|                    | 5.9.3    | Temperature Data Format             |   |

|                    | 5.9.4    | Offset Registers                    |   |

| 5.10               |          | al Zones                            |   |

|                    |          |                                     | _ |

| Chap               |          | Fan Control   2                     |   |

| 6.1                |          | I Description                       |   |

|                    | 6.1.1    | Limit and Configuration Registers 2 |   |

|                    | 6.1.2    | Device Set-Up                       |   |

|                    | 6.1.3    | PWM Fan Speed Control               |   |

|                    | 6.1.4    | Fan Speed Monitoring                | 7 |

# DATASHEET

|     | 6.1.5   | Linking Fan Tachometers to PWMs 43                                                   |

|-----|---------|--------------------------------------------------------------------------------------|

| Cha | pter 7  | Register Set                                                                         |

| 7.1 |         | ned Registers                                                                        |

| 7.2 |         | d Registers                                                                          |

| 1.2 | 7.2.1   | Register 10h: SMSC Test Register                                                     |

|     | 7.2.1   |                                                                                      |

|     |         | Register 1Dh, 1Eh, 1Fh: Offset Registers                                             |

|     | 7.2.3   | Registers 20-24h: Voltage Reading.    48      Devictors 25.07h: Torrespondence    48 |

|     | 7.2.4   | Registers 25-27h: Temperature Reading    49                                          |

|     | 7.2.5   | Registers 28-2Fh: Fan Tachometer Reading                                             |

|     | 7.2.6   | Registers 30-32h: Current PWM Duty                                                   |

|     | 7.2.7   | Register 3Eh: Company ID                                                             |

|     | 7.2.8   | Register 3Fh: Version / Stepping                                                     |

|     | 7.2.9   | Register 40h: Ready/Lock/Start Monitoring 53                                         |

|     | 7.2.10  | Register 41h: Interrupt Status Register 1    54                                      |

|     | 7.2.11  | Register 42h: Interrupt Status Register 2    55                                      |

|     | 7.2.12  | Register 43h: VID                                                                    |

|     | 7.2.13  | Registers 44-4Dh: Voltage Limit Registers 57                                         |

|     | 7.2.14  | Registers 4E-53h: Temperature Limit Registers 57                                     |

|     | 7.2.15  | Registers 54-5Bh: Fan Tachometer Low Limit                                           |

|     | 7.2.16  | Registers 5C-5Eh: PWM Configuration                                                  |

|     | 7.2.17  | Registers 5F-61h: Zone Temperature Range, PWM Frequency                              |

|     | 7.2.18  | Register 62h, 63h: Min/Off, PWM Ramp Rate Control                                    |

|     | 7.2.19  | Registers 64-66h: Minimum PWM Duty Cycle                                             |

|     | 7.2.20  | Registers 67-69h: Zone Low Temperature Limit                                         |

|     | 7.2.21  | Registers 6A-6Ch: Absolute Temperature Limit                                         |

|     | 7.2.22  | Registers 6D-6Eh: Zone Hysteresis Registers                                          |

|     | 7.2.23  | Register 6F: XOR Test Register                                                       |

|     | 7.2.24  | Register 79h: SMSC Test Register                                                     |

|     | 7.2.25  | Register 7Ah: SMSC Test Register                                                     |

|     | 7.2.26  | Register 7Bh: SMSC Test Register                                                     |

|     | 7.2.20  | Register 7Ch: Special Function Register                                              |

|     | 7.2.27  |                                                                                      |

|     |         | Register 7Eh: Interrupt Enable 1 Register                                            |

|     | 7.2.29  | Register 7Fh: Configuration Register   69                                            |

|     | 7.2.30  | Register 80h: Interrupt Enable 2 Register                                            |

|     | 7.2.31  | Register 81h: TACH_PWM Association Register    71                                    |

|     | 7.2.32  | Register 82h: Interrupt Enable 3 Register                                            |

|     | 7.2.33  | Registers 85h-88h: A/D Converter LSbs Registers                                      |

|     | 7.2.34  | Register 89h: SMSC Test Register    73                                               |

|     | 7.2.35  | Registers 8Ah: SMSC Test Register                                                    |

|     | 7.2.36  | Registers 8Bh: SMSC Test Register    73                                              |

|     | 7.2.37  | Registers 8Ch: SMSC Test Register 73                                                 |

|     | 7.2.38  | Registers 8Dh: SMSC Test Register 73                                                 |

|     | 7.2.39  | Registers 8Eh: SMSC Test Register                                                    |

|     | 7.2.40  | Registers 90h-93h: TachX Option Registers                                            |

|     | 7.2.41  | Registers 94h-96h: PWMx Option Registers                                             |

|     | 7.2.42  | Register 97h: SMSC Test Register                                                     |

|     | 7.2.43  | Register 98h:SMSC Test Register                                                      |

|     | 7.2.44  | Register FFh: SMSC Test Register                                                     |

|     |         |                                                                                      |

|     | pter 8  | Operational Description                                                              |

| 8.1 |         | um Guaranteed Ratings                                                                |

| 8.2 | Ratings | s for Operation                                                                      |

|                                      | oter 9 Timing Diagrams                     |    |  |  |  |  |  |

|--------------------------------------|--------------------------------------------|----|--|--|--|--|--|

|                                      | PWM Outputs    8      SMBus Interface    8 |    |  |  |  |  |  |

| Chapter 10 Mechanical Specifications |                                            |    |  |  |  |  |  |

| App                                  | endix AADC Voltage Conversion              | 13 |  |  |  |  |  |

| App                                  | endix B Example Fan Circuits               | 35 |  |  |  |  |  |

# List of Figures

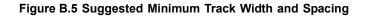

| Figure 2.1  | EMC6D102 Pin Diagram                                      |

|-------------|-----------------------------------------------------------|

| Figure 4.1  | Address Selection on EMC6D102 14                          |

| Figure 5.1  | Interrupt Control                                         |

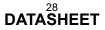

| Figure 6.1  | Automatic Fan Control Flow Diagram                        |

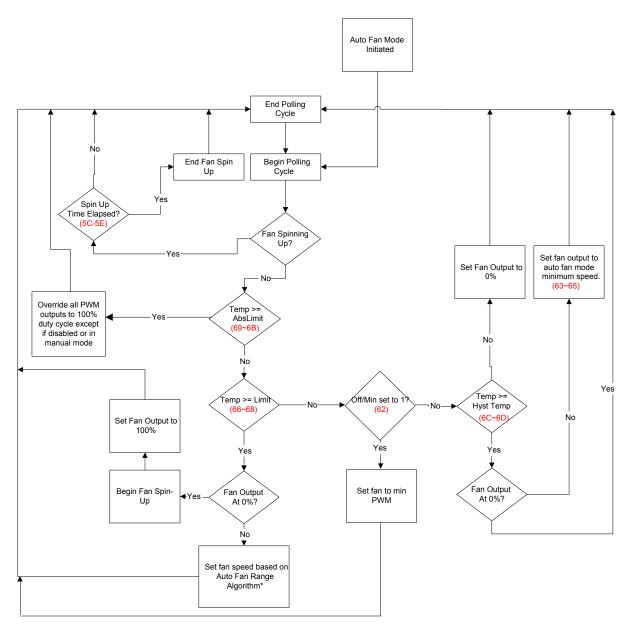

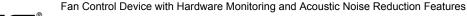

| Figure 6.2  | Automatic Fan Control                                     |

| Figure 6.3  | Spin Up Reduction Enabled                                 |

| Figure 6.4  | Illustration of PWM Ramp Rate Control                     |

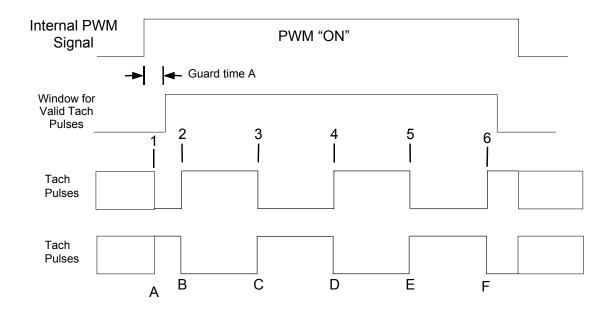

| Figure 6.5  | PWM and Tachometer Concept                                |

| Figure 7.1  | Fan Activity Above Fan Temp Limit                         |

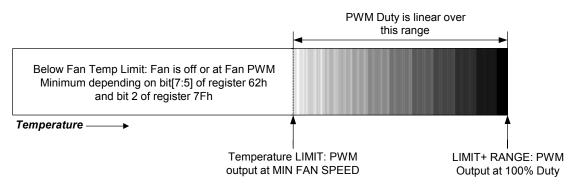

| Figure 9.1  | PWMx Output Timing                                        |

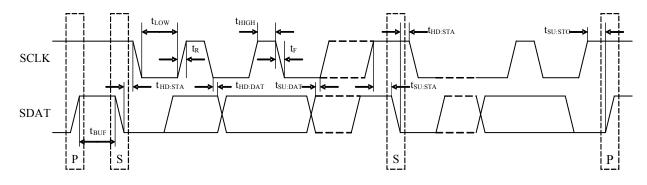

| Figure 9.2  | SMBus Timing                                              |

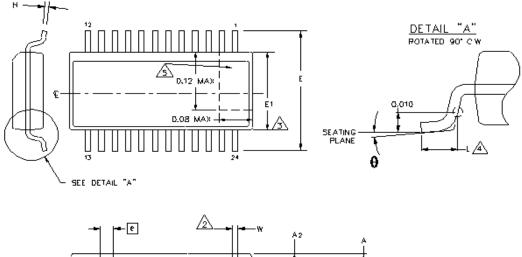

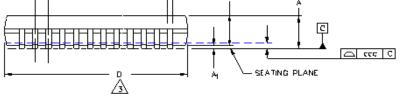

| Figure 10.1 | 24-Pin SSOP Package Outline, 0.150 Wide Body, 0.025 Pitch |

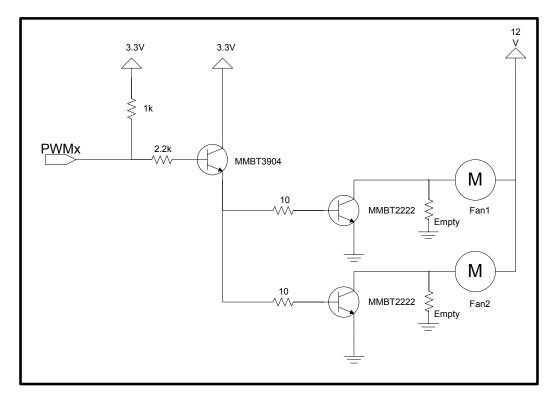

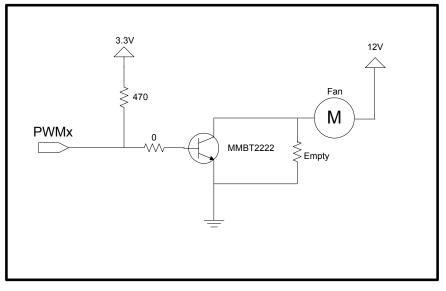

| Figure B.1  | Fan Drive Circuitry (Apply to PWM Driving Two Fans)       |

| Figure B.2  | Fan Drive Circuitry (Apply to PWM Driving One Fan)        |

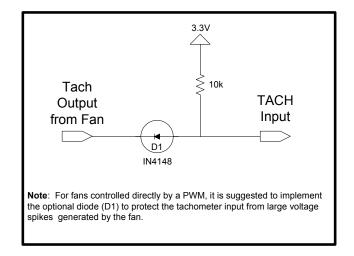

| Figure B.3  | Fan Tachometer Circuitry (Apply to Each Fan)              |

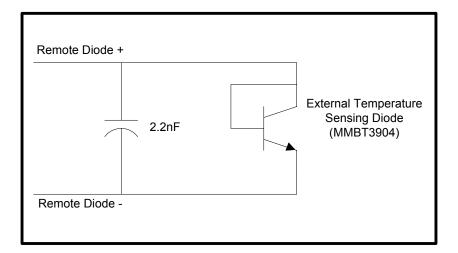

| Figure B.4  | Remote Diode (Apply to Remote2 Lines)                     |

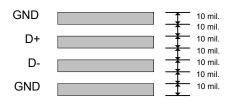

| Figure B.5  | Suggested Minimum Track Width and Spacing                 |

## **List of Tables**

| Table 3.1  | EMC6D102 Pin Description                                             | 10 |

|------------|----------------------------------------------------------------------|----|

| Table 3.2  | Buffer Type Descriptions                                             | 11 |

| Table 4.1  | SMBus Slave Address Options                                          | 13 |

| Table 4.2  | SMBus Write Byte Protocol                                            |    |

| Table 4.3  | SMBus Read Byte Protocol                                             |    |

| Table 4.4  | Modified SMBus Receive Byte Protocol Response to ARA                 |    |

| Table 5.1  | AVG[2:0] Bit Decoder                                                 |    |

| Table 5.2  | Conversion Cycle Timing.                                             | 19 |

|            | ADC Conversion Sequence                                              |    |

|            | Low Power Mode Control Bits                                          |    |

|            | Min/Max ADC Conversion Table                                         |    |

|            | Temperature Data Format                                              |    |

| Table 6.1  | PWM Ramp Rate                                                        |    |

| Table 6.2  |                                                                      |    |

| Table 6.3  | Minimum RPM Detectable Using 3 Edges – No PWM Stretching             | 41 |

| Table 6.4  | Minimum RPM Detectable Using 2 Edges – No PWM Stretching             | 42 |

| Table 6.5  | Minimum RPM Detectable– With PWM Stretching                          | 43 |

| Table 7.1  | Register Summary                                                     |    |

| Table 7.2  | Voltage vs. Register Reading                                         | 49 |

| Table 7.3  | Temperature vs. Register Reading                                     | 50 |

| Table 7.4  | PWM Duty vs Register Reading                                         | 52 |

| Table 7.6  | Temperature Limits vs. Register Settings                             | 58 |

|            | Fan Zone Setting                                                     |    |

|            | Fan Spin-Up Register                                                 |    |

| Table 7.9  | Register Setting vs. PWM Frequency                                   | 61 |

| Table 7.10 | Register Setting vs. Temperature Range                               | 62 |

| Table 7.11 | PWM output below Limit depending on value of Off/Min                 | 62 |

| Table 7.12 | PWM Ramp Rate Control                                                | 63 |

| Table 7.13 | PWM Duty vs. Register Setting                                        | 64 |

| Table 7.14 | Temperature Limit vs. Register Setting                               | 65 |

|            | Absolute Limit vs. Register Setting                                  |    |

|            | Hysteresis Settings                                                  |    |

|            | AVG[2:0] Bit Decoder                                                 |    |

|            | Timing for PWM[1:3] Outputs                                          |    |

|            | 24-pin SSOP Package Parameters                                       |    |

| Table A.1  | Analog-to-Digital Voltage Conversions for Hardware Monitoring Block. | 83 |

# **Chapter 1 General Description**

The EMC6D102 is an environmental monitoring device with automatic fan control capability. This ACPI compliant device provides hardware monitoring for up to five voltages and three thermal zones, measures the speed of up to four fans, and controls the speed of multiple DC fans using Pulse Width Modulator (PWM) outputs.

The EMC6D102 hardware monitor provides analog inputs for monitoring external voltages of +2.5V, +5V, +12V and Vccp. This device has the capability to monitor its own internal VCC power supply, which may be connected to either main power (VCC) or the suspend power well (VTR). In addition to monitoring the processor voltage, VID inputs are available to identify the voltage specification. External components are not required for voltage scaling or similar treatment.

The EMC6D102 hardware monitor includes support for monitoring three thermal zones: two external and one internal. The external temperatures are measured via thermal diode inputs capable of monitoring remote devices. In addition, they are equipped with an ambient temperature sensor for measuring the internal temperature.

Pulse Width Modulators (PWM) control the speed of the fans by varying the output duty cycle of the PWM. Each PWM can be associated with any or all of the thermal zones monitored. As the temperature of the associated zone varies, the PWM duty cycle is adjusted accordingly. The Ramp Rate Control feature controls the rate of change of the PWM output, thereby reducing system noise created by changing the fan speed. The speed of each fan is monitored by a Fan Tachometer input. The measured values are compared to values stored in Limit Registers to detect if a fan has stalled or seized.

Fan speed may be under host software control or automatic. In host control mode, the host software continuously monitors temperature and fan speed registers, makes decisions as to desired fan speed and sets the PWM's to drive the required fan speed. This device offers an interrupt output signal (INT#), which may be used to interrupt the host on out-of-limit temperature or voltage condition enabling an ACPI response as opposed to the host software continuously monitoring status. In auto "zone" mode, the logic continuously monitors the temperature and fan speeds and adjusts speeds without intervention from the host CPU. Fan speed is adjusted according to an algorithm using the temperature measured in the selected zone, the high and low limits set by the user, and the current fan speed.

# **Chapter 2 Pinout**

This Environmental Monitoring and Control device (EMC) is offered in a 24 pin SSOP mechanical package.

The EMC6D102 is a 24 pin SSOP.

Figure 2.1 EMC6D102 Pin Diagram

# **Chapter 3 Pin Description**

## 3.1 Pin Functions

| NAME                                                                                                                                | FUNCTION                                                                                                                                       | BUFFER<br>TYPE     | BUFFER<br>REQUIREMENT<br>PER FUNCTION<br>(Note 3.1) | POWER<br>WELL | NOTES    |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------|---------------|----------|

|                                                                                                                                     | HARDWARE MONITOR                                                                                                                               |                    | . ,                                                 |               |          |

| SDA                                                                                                                                 | System Management Bus bi-directional Data.<br>Open Drain output.                                                                               | I <sub>M</sub> OD3 | I <sub>M</sub> OD3                                  | VCC           |          |

| SCLK                                                                                                                                | System Management Bus Clock.                                                                                                                   | ۱ <sub>M</sub>     | ۱ <sub>M</sub>                                      | VCC           |          |

| VID0                                                                                                                                | Voltage ID 0 Input                                                                                                                             | ۱ <sub>M</sub>     | ١ <sub>M</sub>                                      | VCC           |          |

| VID1                                                                                                                                | Voltage ID 1 Input                                                                                                                             | ۱ <sub>M</sub>     | ١ <sub>M</sub>                                      | VCC           |          |

| VID2                                                                                                                                | Voltage ID 2 Input                                                                                                                             | ۱ <sub>M</sub>     | ١ <sub>M</sub>                                      | VCC           |          |

| VID3                                                                                                                                | Voltage ID 3 Input                                                                                                                             | ۱ <sub>M</sub>     | I <sub>M</sub>                                      | VCC           |          |

| VID4                                                                                                                                | Voltage ID 4 Input                                                                                                                             | ۱ <sub>M</sub>     | ۱ <sub>M</sub>                                      | VCC           |          |

| Remote1-                                                                                                                            | This is the negative Analog input (current sink) from the remote thermal diode. This serves as the negative input into the A/D. Digital Input. | I <sub>AN</sub>    | I <sub>AN</sub>                                     | VCC           |          |

| Remote1+                                                                                                                            | This is the positive input (current source) from the remote thermal diode. This serves as the positive input into the A/D.                     | I <sub>AN</sub>    | I <sub>AN</sub>                                     | VCC           |          |

| Remote2-                                                                                                                            | This is the negative Analog input (current sink) from the remote thermal diode. This serves as the negative input into the A/D. Digital Input. | I <sub>AN</sub>    | I <sub>AN</sub>                                     | VCC           |          |

| Remote2+ This is the positive input (current source) from the remote thermal diode. This serves as the positive input into the A/D. |                                                                                                                                                | I <sub>AN</sub>    | I <sub>AN</sub>                                     | VCC           |          |

| +5V_IN                                                                                                                              | Analog input for +5V                                                                                                                           | I <sub>AN</sub>    | I <sub>AN</sub>                                     | VCC           | Note 3.2 |

| +2.5V_IN                                                                                                                            | Analog input for +2.5V                                                                                                                         | I <sub>AN</sub>    | I <sub>AN</sub>                                     | VCC           | Note 3.2 |

| Vccp                                                                                                                                | Analog input for +Vccp (processor voltage: 0 to 3.0V).                                                                                         | I <sub>AN</sub>    | I <sub>AN</sub>                                     | VCC           | Note 3.2 |

| 12V_IN                                                                                                                              | Analog input for +12V                                                                                                                          | I <sub>AN</sub>    | I <sub>AN</sub>                                     | VCC           | Note 3.2 |

## Table 3.1 EMC6D102 Pin Description

| NAME                        | FUNCTION                                                                                                                                                                | BUFFER<br>TYPE     | BUFFER<br>REQUIREMENT<br>PER FUNCTION<br>(Note 3.1) | POWER<br>WELL | NOTES |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------|---------------|-------|

| TACH1                       | Input for monitoring a fan tachometer input.                                                                                                                            | ۱ <sub>M</sub>     | ۱ <sub>M</sub>                                      | VCC           |       |

| TACH2                       | Input for monitoring a fan tachometer input.                                                                                                                            | ۱ <sub>M</sub>     | ۱ <sub>M</sub>                                      | VCC           |       |

| TACH3<br>/INT#              | Input for monitoring a fan tachometer input.<br>/Interrupt output to indicate a thermal and/or<br>voltage event.                                                        | I <sub>M</sub> OD3 | I <sub>M</sub> /OD3                                 | VCC           |       |

| TACH4<br>/Address<br>Select | Input for monitoring a fan tachometer input.<br>If in Address Select Mode, determines the<br>SMBus address of the device.                                               | ۱ <sub>M</sub>     | Ι <sub>Μ</sub>                                      | VCC           |       |

| PWM1<br>/xTest Out          | PWM Output 1 controlling speed of fan.<br>When in XOR tree test mode, functions as<br>XOR Tree output.                                                                  | O8                 | OD8/O8                                              | VCC           |       |

| PWM2<br>/INT#               | PWM Output 2 controlling speed of fan.<br>/Interrupt output to indicate a thermal and/or<br>voltage event.                                                              | OD8                | OD8/OD8                                             | VCC           |       |

| PWM3<br>/Address<br>Enable# | PWM Output 3 controlling speed of fan.<br>If pulled to ground at power on, enables<br>Address Select Mode (Address Select pin<br>controls SMBus address of the device). | IOD8               | OD8/I                                               | VCC           |       |

| VCC                         | Positive Power Supply. Nominal 3.3V.<br>VCC is monitored by the Hardware<br>Monitoring Block.                                                                           |                    |                                                     |               |       |

|                             | (Can be powered by +3.3V Standby power if monitoring in low power states is required.)                                                                                  |                    |                                                     |               |       |

| VSS                         | Analog Ground.                                                                                                                                                          |                    |                                                     |               |       |

Note: The "#" as the suffix of a signal name indicates an "Active Low" signal.

**Note 3.1** Buffer types per function on multiplexed pins are separated by a slash "*l*". Buffer types in parenthesis represent multiple buffer types for a single pin function.

**Note 3.2** This analog input is backdrive protected.

## 3.2 Buffer Type Description

**Note:** The buffer type values are specified at VCC=3.3V

## Table 3.2 Buffer Type Descriptions

| BUFFER TYPE        | DESCRIPTION                              |  |  |  |

|--------------------|------------------------------------------|--|--|--|

| I <sub>M</sub>     | Digital Input                            |  |  |  |

| I <sub>AN</sub>    | Analog Input, Hardware Monitoring Block. |  |  |  |

| I <sub>M</sub> OD3 | Input/Output (Open Drain), 3mA sink.     |  |  |  |

| O8                 | Output, 8mA sink, 4mA source.            |  |  |  |

| OD8                | Output (Open Drain), 8mA sink.           |  |  |  |

| IO8                | Input/Output, 8mA sink, 4mA source.      |  |  |  |

## 3.3 3.3V Operation, 5V Tolerance

The EMC6D102 is intended to operate with a nominal 3.3V power supply. The analog voltage pins are connected to voltage sources at their respective nominal levels. All digital signal pins are 3V switching, but are tolerant to 5V.

# Chapter 4 SMBus Interface

The host processor communicates with the Fan Monitoring device through a series of read/write registers via the SMBus interface. SMBus is a serial communication protocol between a computer host and its peripheral devices.

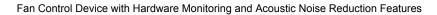

## 4.1 Slave Address

The default Slave Address is 0101110b. If this address is desired, the designer should not ground the Address Enable# pin and should not apply a strapping resistor to the Address Select pin.

If multiple devices are implemented in a system or another SMBus device requires address 0101110b, TACH4 and PWM3 must be disabled. In this case, addressing is implemented as follows:

The board designer will apply a  $10K\Omega$  pull-down resistor to ground on the Address Enable# pin. Upon power up, the EMC6D102 device will be placed into Address Enable mode and assign itself an SMBus address according to the Address Select input. The device will latch the address during the first valid SMBus transaction in which the first five bits of the targeted address match those of the EMC6D102 address. This feature eliminates the possibility of a glitch on the SMBus interfering with address selection.

| ADDRESS<br>ENABLE# | ADDRESS<br>SELECT | BOARD IMPLEMENTATION                                                                                                            | SMBUS ADDRESS [7:1]    |

|--------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1                  | х                 | Address Enable# pulled to VCC through resistor<br><b>Note:</b> Resistor value will be dependent on PWM<br>circuit implemented.  | 0101 110b<br>(default) |

| 0                  | 0                 | Address Enable# pulled to ground through $10k\Omega$ resistor<br>Address Select Pulled to ground through a $10k\Omega$ resistor | 0101 100b              |

| 0                  | 1                 | Address Enable# pulled to ground through $10k\Omega$ resistor<br>Address Select pulled to VCC through a $10k\Omega$ resistor    | 0101 101b              |

## Table 4.1 SMBus Slave Address Options

In this way, there can be up to three EMC6D102 devices on the SMBus at any time. Multiple EMC6D102 devices can be used to monitor additional processors and temperature zones.

Figure 4.1 Address Selection on EMC6D102

## 4.2 Slave Bus Interface

The EMC6D102 device SMBus implementation is a subset of the SMBus interface to the host. The device is a *slave-only* SMBus device. The implementation in the device is a subset of SMBus since it only supports four protocols.

The Write Byte and Read Byte protocols are valid SMBus protocols for the device. This part responds to other protocols as described in the Invalid Protocol Section. Reference the System Management Bus Specification, Rev 2.0.

The SMBus interface is used to read and write the registers in the device. The register set is shown in section 11 Register Set on page 31.

## 4.3 Bus Protocols

Typical Write Byte and Read Byte protocols are shown below. Register accesses are performed using 7-bit slave addressing, an 8-bit register address field, and an 8-bit data field. The shading indicates the Hardware Monitor Block driving data on the SDA line; otherwise, host data is on the SDA line.

The slave address is the unique SMBus Interface Address for the Hardware Monitor Block that identifies it on SMBus. The register address field is the internal address of the register to be accessed. The register data field is the data that the host is attempting to write to the register or the contents of the register that the host is attempting to read.

Note: Data bytes are transferred MSB first.

## **Byte Protocols**

A write byte transfer will always consist of three bytes of information being transferred: the SMBus Interface Address byte, followed by the Internal Address Register byte, and finally the data byte. A read byte consists of four bytes of information being transferred. The first three bytes are written by the host device and the last byte is the byte returned by the hardware monitoring block. The bytes of information being transferred during a read byte command are: the SMBus Interface Address byte, followed by the Internal Address Register byte, a repeated SMBus Interface Address byte, and finally the data byte.

**Note:** The SMBus controller detects the repeated START condition that is generated before the repeated SMBus Interface Address byte to distinguish between a write byte protocol and a read byte protocol. See the following sections for a more detailed description of each of these protocols.

#### Write Byte

The Write Byte protocol is used to write data to the registers. The data will only be written if the protocol shown in Table 4.2 is performed correctly. Only one byte is transferred at time for a Write Byte protocol.

#### Table 4.2 SMBus Write Byte Protocol

| FIELD | START | SLAVE ADDR | WR | АСК | REG. ADDR | АСК | REG. DATA | АСК | STOP |

|-------|-------|------------|----|-----|-----------|-----|-----------|-----|------|

| Bits  | 1     | 7          | 1  | 1   | 8         | 1   | 8         | 1   | 1    |

#### **Read Byte**

The Read Byte protocol is used to read data from the registers. The data will only be read if the protocol shown in Table 4.3 is performed correctly. Only one byte is transferred at time for a Read Byte protocol.

| FIELD: | START | SLAVE<br>ADDR | WR | АСК | REG.<br>ADDR | АСК | START | SLAVE<br>ADDR | RD | АСК | REG.<br>DATA | NACK | STOP |

|--------|-------|---------------|----|-----|--------------|-----|-------|---------------|----|-----|--------------|------|------|

| Bits:  | 1     | 7             | 1  | 1   | 8            | 1   | 1     | 7             | 1  | 1   | 8            | 1    | 1    |

## 4.4 Invalid Protocol Response Behavior

Registers that are accessed with an invalid protocol will not be updated. A register will only be updated following a valid protocol. The only valid protocols are the Write Byte and Read Byte protocols, which are described above.

The EMC6D102 device responds to three SMBus slave addresses:

- The SMBus slave address that supports the valid protocols defined in the previous sections is determined by the level on the Address Select and Address Enable pins as shown in Section 4.1, "Slave Address," on page 13.

- SMBus Alert Response (0001 100). The SMBus will only respond to the SMBus Alert Response Address if the SMBus Alert Response interrupt was generated to request a response from the Host. The SMBus Alert Response is defined in Section 4.10, "SMBus Alert Response Address," on page 16.

Attempting to communicate with the Hardware Monitor Block over SMBus with an invalid slave address, or invalid protocol will result in no response, and the SMBus Slave Interface will return to the idle state.

The only valid registers that are accessible by the SMBus slave address are the registers defined in the Registers Section. See Section 4.4.1, "Undefined Registers" for response to undefined registers.

## 4.4.1 Undefined Registers

Reads to undefined registers return 00h. Writes to undefined registers have no effect and return no error.

## 4.5 General Call Address Response

The EMC6D102 will not respond to a general call address of 0000\_000.

## 4.6 Slave Device Time-Out

The EMC6D102 supports the slave device timeout as per the SMBus Specification, v2.0.

According to SMBus specification, v2.0 devices in a transfer can abort the transfer in progress and release the bus when any single clock low interval exceeds 25ms ( $T_{TIMEOUT, MIN}$ ). Devices that have detected this condition must reset their communication and be able to receive a new START condition no later than 35ms ( $T_{TIMEOUT, MAX}$ ).

**Note:** Some simple devices do not contain a clock low drive circuit; this simple kind of device typically may reset its communications port after a start or stop condition.

## 4.7 Stretching the SCLK Signal

The EMC6D102 supports stretching of the SCLK by other devices on the SMBus. The Hardware Monitor Block does not stretch the SCLK.

## 4.8 SMBus Timing

The SMBus Slave Interface complies with the SMBus AC Timing Specification. See the SMBus timing diagram shown in the section titled Section 9.2, "SMBus Interface," on page 80.

## 4.9 Bus Reset Sequence

The SMBus Slave Interface will reset and return to the idle state upon a START field followed immediately by a STOP field.

## 4.10 SMBus Alert Response Address

The EMC6D102 device responds to the SMBus Alert Response Address, 0001 100, if the INTEN bit (register 7Ch bit 2) is set and one or more status events bits are high. The interrupt signal (INT#), which can be enabled on either the PWM2 or TACH3 pins, can be used as the SMBALERT#. See the section describing the Interrupt Status Registers on page 21 and the section describing the Interrupt Pin on page 23 for more details on interrupts.

The device can signal the host that it wants to talk by pulling the SMBALERT# low, if a status bit is set in one of the interrupt status registers and properly enabled onto the INT# pin. The host processes the interrupt and simultaneously accesses all SMBALERT# devices through a modified Receive Byte operation with the Alert Response Address (ARA).

The EMC6D102 device, which pulled SMBALERT# low, will acknowledge the Alert Response Address and respond with its device address. The 7-bit device address provided by the EMC6D102 device is placed in the 7 most significant bits of the byte. The eighth bit can be a zero or one.

| FIELD: | START | ALERT<br>RESPONSE<br>ADDRESS | RD | ACK | EMC6D102 SLAVE<br>ADDRESS | NACK | STOP |

|--------|-------|------------------------------|----|-----|---------------------------|------|------|

| Bits:  | 1     | 7                            | 1  | 1   | 8                         | 1    | 1    |

## Table 4.4 Modified SMBus Receive Byte Protocol Response to ARA

After acknowledging the slave address, the EMC6D102 device will disengage the SMBALERT# pulldown by clearing the INT enable bit. If the condition that caused the interrupt remains, the Fan Control device will reassert the SMBALERT# on the next monitoring cycle, provided the INT enable bit has been set back to '1' by software.

**Note:** The INT# signal is an alternate function on the PWM2 and TACH3 pins. The EMC6D102 device will respond to the SMBus Alert Response address even if the INT# signal is not selected as the alternate function on one of these pins as long as the following conditions exist: the INTEN bit (register 7Ch bit 2) is set, an individual status bit is set in one of the interrupt status registers, and the corresponding group enable bit is set. Each interrupt event must be enabled into the interrupt status registers, and the status bits must be enabled onto the INT# signal via the group enable bits for each type of event (i.e., temperature, voltage and fan). See the section titled Interrupt Status Registers on page 21.

# Chapter 5 Hardware Monitoring

The following sub-sections describe the EMC6D102 Hardware Monitoring features.

## 5.1 Input Monitoring

The EMC6D102 device's monitoring function is started by writing a '1' to the START bit in the **Ready/Lock/Start** Register (0x40). Measured values from the analog inputs and temperature sensors are stored in Reading Registers. The values in the reading registers can be accessed via the SMBus interface. These values are compared to the programmed limits in the Limit Register. The out-of-limit and diode fault conditions are stored in the Interrupt Status Registers.

## 5.2 Resetting the EMC6D102

## 5.2.1 Power-On Reset

All the registers in the Hardware Monitor Block, except the reading registers, reset to a default value when power is applied to the block. The default state of the register is shown in the table in the Register Summary subsection. The default state of Reading Registers are not shown because these registers have indeterminate power on values.

**Note:** Usually the first action after power up is to write limits into the Limit Registers.

## 5.2.2 Soft Reset (Initialization)

Setting bit 7 of the CONF register performs a soft reset. This bit is self-clearing. Soft Reset performs reset on all the registers except the Reading Registers.

## 5.3 Monitoring Modes

The Hardware Monitor Block supports two Monitoring modes: Continuous Mode and Cycle Mode. These modes are selected using bit 1 of the Special Function Register (7Ch). The following subsections contain a description of these monitoring modes.

The hardware monitor conversion clock is 45KHz  $\pm 10\%$ . Temperature conversions take 96 clocks, each (2.133ms nom.); voltage conversions take 68 clocks, each (1.511ms nom). The time to complete a conversion cycle depends upon the number of inputs in the conversion sequence to be measured (see Table 5.3, "ADC Conversion Sequence," on page 20) and the amount of averaging per input, which is selected using the AVG[2:0] bits in the Special Function register (see Register 7Ch: Special Function Register on page 68).

For each mode, there are four options for the number of measurements that are averaged for each temperature and voltage reading. These options are selected using bits[7:5] of the Special Function register (7Ch). These bits are defined as follows:

## Bits [7:5] AVG[2:0]

The AVG[2:0] bits determine the amount of averaging for each of the measurements that are performed by the hardware monitor before the reading registers are updated (Table 5.1). The AVG[2:0] bits are priority encoded where the most significant bit has highest priority. For example, when the AVG2 bit is asserted, 32 averages will be performed for each measurement before the reading registers are updated regardless of the state of the AVG[1:0] bits.

## Table 5.1 AVG[2:0] Bit Decoder

|      | SFTR[7:5] |      | MEASUREMENTS PER READING |                   |                   |                                                           |  |

|------|-----------|------|--------------------------|-------------------|-------------------|-----------------------------------------------------------|--|

| AVG2 | AVG1      | AVG0 | REMOTE<br>DIODE 1        | REMOTE<br>DIODE 2 | INTERNAL<br>DIODE | ALL VOLTAGE READINGS<br>(+2.5V, +5V, +12V, VCCP, AND VCC) |  |

| 0    | 0         | 0    | 128                      | 128               | 8                 | 8                                                         |  |

| 0    | 0         | 1    | 16                       | 16                | 1                 | 1                                                         |  |

| 0    | 1         | Х    | 16                       | 16                | 16                | 16                                                        |  |

| 1    | Х         | Х    | 32                       | 32                | 32                | 32                                                        |  |

Note: The default for the AVG[2:0] bits is '010'b.

To calculate conversion cycle timing for a given averaging mode:

- Compute total number of temperature conversions (TEMP\_CONV)

- Compute total number of voltage conversions (VOLT\_CONV)

- Calculate Time to complete all conversions is:

Total Conversion Time = (TEMP\_CONV)\*96/(45kHz +/-10%)+ (VOLT\_CONV)\*68/(45kHz +/-10%)

## Example: To calculate the nominal conversion time FOR AVG[2:0] = 001b.

Total Conversion Time = (TEMP\_CONV)\*96/(45kHz)+ (VOLT\_CONV)\*68/(45kHz)

Total Conversion Time = (16+16+1)\*96/(45kHz)+ (5\*1)\*68/(45kHz)

Total Conversion Time = (33)\*2.133ms+ (5)\*1.511ms = ~78ms

Table 5.2 illustrates the min., nom., and max. conversion cycle timing for each of the four averaging modes.

|               | TOTAL                      | TOTAL                  | CONVERSION CYCLE TIME (MSEC) |      |      |  |

|---------------|----------------------------|------------------------|------------------------------|------|------|--|

| AVG[2:0]      | TEMPERATURE<br>CONVERSIONS | VOLTAGE<br>CONVERSIONS | MIN.                         | NOM. | MAX. |  |

| 000           | (2x128)+(1x8)=264          | 5x8=40                 | 567                          | 624  | 693  |  |

| 001           | (2x16)+(1x1)=33            | 5x1=5                  | 71                           | 78   | 87   |  |

| 01X (default) | 3x16=48                    | 5x16=80                | 203                          | 223  | 248  |  |

| 1XX           | 3x32=96                    | 5x32=160               | 406                          | 447  | 496  |  |

Table 5.2 Conversion Cycle Timing

#### Notes:

- The hardware monitor conversion clock is 45KHz ± 10%.

- Temperature conversions take 96 clocks, each (2.133ms nom.); Voltage conversions take 68 clocks, each (1.511ms nom).

## 5.3.1 Continuous Monitoring Mode

In the continuous monitoring mode, the sampling and conversion process is performed continuously for each voltage and temperature reading after the Start bit is set high. The time for each voltage and temperature reading is shown above for each measurement option.

The continuous monitoring function is started by doing a write to the Ready/Lock/Start Register, setting the Start bit (Bit 0) high. The part then performs a "round robin" sampling of the inputs, in the order shown below (see Table 5.3). Sampling of all values occurs in a nominal 223 ms (default - see Table 5.2, "Conversion Cycle Timing," on page 19).

| Table 5.3 ADC Conversion Sequence |  |

|-----------------------------------|--|

|-----------------------------------|--|

| SAMPLING ORDER | REGISTER                    |  |  |

|----------------|-----------------------------|--|--|

| 1              | Remote Diode Temp Reading 1 |  |  |

| 2              | Ambient Temperature reading |  |  |

| 3              | VCC reading                 |  |  |

| 4              | +12V reading                |  |  |

| 5              | +5V reading                 |  |  |

| 6              | +2.5V reading               |  |  |

| 7              | Vccp (processor) reading    |  |  |

| 8              | Remote Diode Temp Reading 2 |  |  |

When the continuous monitoring function is started, it cycles through each measurement in sequence, and it continuously loops through the sequence approximately once every 223 ms (default - see Table 5.2, "Conversion Cycle Timing," on page 19). Each measured value is compared to values stored in the Limit registers. When the measured value violates the programmed limit the Hardware Monitor Block will set a corresponding status bit in the Interrupt Status Registers.

If auto fan option is selected, the hardware will adjust the operation of the fans accordingly. See Auto Fan Control Operating Mode on page 30.

The results of the sampling and conversions can be found in the Reading Registers and are available at any time.

## 5.3.2 Cycle Monitoring Mode

In cycle monitoring mode, the part completes all sampling and conversions, then waits approximately one second to repeat the process. It repeats the sampling and conversion process typically every 1.2 seconds (1.4 sec max - default averaging enabled). The sampling and conversion of each voltage and temperature reading is performed once every monitoring cycle. This is a power saving mode.

The cycle monitoring function is started by doing a write to the Ready/Lock/Start Register, setting the Start bit (Bit 0) high. The part then performs a "round robin" sampling of the inputs, in the order shown above.

When the cycle monitoring function is started, it cycles through each measurement in sequence, and it produces a converted voltage and temperature reading for each input. The state machine waits approximately one second before repeating this process. Each measured value is compared to values stored in the Limit registers. When the measured value violates (or is equal to) the programmed limit the Hardware Monitor Block will set a corresponding status bit in the Interrupt Status Registers.

If auto fan option is selected, the hardware will adjust the operation of the fans accordingly. See the section titled Auto Fan Control Operating Mode on page 30.

The results of each sampling and conversion can be found in the Reading Registers and are available at any time, however, they are only updated once per conversion cycle.

## 5.4 Interrupt Status Registers

The Hardware Monitor Block contains two interrupt status registers: Register 41h: Interrupt Status Register 1 on page 54 and on page 55. These registers are used to reflect the state of all temperature, voltage and fan violation of limit error conditions and diode fault conditions that the Hardware Monitor Block monitors.

When an error occurs during the conversion cycle, its corresponding bit is set in its respective interrupt status register. The bit remains set until the register is read by software, at which time the bit will be cleared to '0' if the associated error event no longer violates the limit conditions or if the diode fault condition no longer exists. Reading the register will not cause a bit to be cleared if the source of the status bit remains active.

These registers are read only -a write to these registers have no effect. These registers default to 0x00 on VCC POR and Initialization.

See the description of the Interrupt Status registers in Chapter 7, "Register Set," on page 45.

Each interrupt status bit has a corresponding bit located in an interrupt enable register, which may be used to enable/disable the individual event from setting the status bit. See the figure below for the status and enable bits used to control the interrupt bits and INT# pin.

## Figure 5.1 Interrupt Control

**Note:** The diode fault bits are not mapped directly to the INT# pin. A diode fault condition forces the diode reading register to a value of 80h, which will generate a Diode Error condition. See section Diode Fault on page 22.

## 5.4.1 Diode Fault

The EMC6D102 Chip automatically sets the associated diode fault bit to 1 when any of the following conditions occur on the Remote Diode pins:

- The positive and negative terminal are an open circuit.

- Positive terminal is connected to VCC

- Positive terminal is connected to ground

- Negative terminal is connected to VCC

Negative terminal is connected to ground

The occurrence of a fault will cause 80h to be loaded into the associated reading register, except for the case when the negative terminal is connected to ground. A temperature reading of 80h will cause the corresponding diode error bit to be set. This will cause the INT# pin to become active if the individual, group (TEMP), and global enable (INTEN) bits are set.

#### Notes:

- The individual remote diode enable bits and the TEMP bit are located in on page 69. The INTEN bit is located in bit[2] of on page 68.

- When 80h is loaded into the Remote Diode Reading Register the PWM output(s) controlled by the zone associated with that diode input will be forced to full on. See Thermal Zones on page 27.

If the diode is disabled, the fault bit in the interrupt status register will not be set. In this case, the occurrence of a fault will cause 00h to be loaded into the associated reading register. The limits must be programmed accordingly to prevent unwanted fan speed changes based on this temperature reading. If the diode is disabled and a fault condition does not exist on the diode pins, then the associated reading register will contain a "valid" reading.

## 5.5 Interrupt Pin

The INT# function is used as an interrupt output for out-of-limit temperature, voltage events, and/or fan errors.

The INT# signal can be enabled onto the PWM2 or the TACH3 pins.

To configure the PWM2/INT# pin for the interrupt function, set bit[1] P2INT of the CONF register (7Fh) to '1'

To configure the TACH3/INT# pin for the interrupt function, set bit[0] T3INT of the CONF register (7Fh) to '1'

To enable the interrupt pin to go active, set bit 2 of the Special Function Register (7Ch) to '1'.

To enable temperature event, voltage events and/or fan events onto the INT# pin:

- To enable out-of-limit temperature events set bit[0] of the Interrupt Enable 3 (TEMP) register (82h) to '1'.

- To enable out-of-limit voltage events set bit[0] of the Interrupt Enable 1(VOLT) register (7Eh) to '1'

- To enable Fan tachometer error events set bit[0] of the Interrupt Enable 2(Fan Tachs) register (80h) to '1'.

See Figure 5.1 on page 22. The following description assumes that the interrupt enable bits for all events are set to enable the interrupt status bits to be set.

If the internal or remote temperature reading violates the low or high temperature limits, INT# will be forced active low (if all the corresponding enable bits are set: individual enable bits (D1\_EN, D2\_EN, and/or AMB\_EN), group enable bit (TEMP\_EN) and the global enable bit (INTEN)). This pin will remain low while the Internal Temp Error bit or one or both of the Remote Temp Error bits in Interrupt Status 1 Register is set and the enable bit is set.

The INT# pin will not become active low as a result of the remote diode fault bits becoming set. However, the occurrence of a fault will cause 80h to be loaded into the associated reading register, which will cause the corresponding diode error bit to be set. This will cause the INT# pin to become active if enabled.

The INT# pin can be enabled to indicate out-of-limit voltages. Bit[0] of the Interrupt Enable 1(VOLT) register (7Eh) is used to enable this option. When this bit is set, if one or more of the voltage readings violates the low or high limits, INT# will be forced active low (if all the corresponding enable bits are set: individual enable bits (VCC\_Error\_En, 12V\_Error\_En, 5V\_Error\_En, 33V\_Error\_En, VCCP\_Error\_En, 25V\_Error\_En, 18V\_Error\_En, and/or 15V\_Error\_En), group enable (VOLT\_EN), and global enable (INT\_EN)). This pin will remain low while the associated voltage error bit in the Interrupt Status Register 1 or Interrupt Status Register 2 is set.

The INT# pin can be enabled to indicate fan errors. Bit[0] of the Interrupt Enable 2(Fan Tachs) register (80h) is used to enable this option. This pin will remain low while the associated fan error bit in the Interrupt Status Register 2 is set.

The INT# pin will remain low while any bit is set in any of the Interrupt Status Registers. Reading the interrupt status registers will cause the logic to attempt to clear the status bits; however, the status bits will not clear if the interrupt stimulus is still active. The interrupt enable bit (Special Function Register bit[2]) should be cleared by software before reading the interrupt status registers to insure that the INT# pin will be re-asserted while an interrupt event is active, when the INT\_EN bit is written to '1' again.

The INT# pin can also be deasserted by issuing an Alert Response Address Call. See the description in the section titled SMBus Alert Response Address on page 16.

The INT# pin may only become active while the monitor block is operational.

## 5.6 Low Power Modes

The Hardware Monitor Block can be placed in a low-power mode by writing a '0' to Bit[0] of the Ready/Lock/Start Register (0x40). The low power mode that is entered is either sleep mode or shutdown mode as selected using Bit[0] of the Special Function Register (7Ch). These modes do not reset any of the registers of the Hardware Monitor Block. In both of these modes, the PWM pins are at 100% duty cycle.

| START | LPMD | DESCRIPTION   |

|-------|------|---------------|

| 0     | 0    | Sleep Mode    |

| 0     | 1    | Shutdown Mode |

| 1     | Х    | Monitoring    |

#### Table 5.4 Low Power Mode Control Bits

#### Notes:

- START and LPMD bits cannot be modified when the LOCK bit is set.

- START bit is located in the Ready/Lock/Start register (40h). LPMD bit is located in the Special Function Register (7Ch)

## 5.6.1 Sleep Mode

This is a low power mode in which bias currents are on and the internal oscillator is on, but the the A/D converter and monitoring cycle are turned off. Serial bus communication is still possible with any register in the Hardware Monitor Block while in this low-power mode.

## 5.6.2 Shutdown Mode

This is a low power mode in which bias currents are off, the internal oscillator is off, and the the A/D converter and monitoring cycle are turned off. Serial communication is only possible with Bits[2:0] of the Special Function Register at 7Ch and Bits [7:0] of the Configuration Register at 7Fh, which become write-only registers in this mode.

## 5.7 Analog Voltage Measurement

The Hardware Monitor Block contains inputs for directly monitoring the power supplies (+12 V, +5 V, +2.5V, +Vccp, and VCC). These inputs are scaled internally to an internal reference source, converted via an 8 bit successive approximation register ADC or a Delta-Sigma ADC (Analog-to-Digital Converter), and scaled such that the correct value refers to 3/4 scale or 192 decimal (except the Vccp input). This removes the need for external resistor dividers and allows for a more accurate means of measurement since the voltages are referenced to a known value. Since any of these inputs can be

above VCC or below Ground, they are not diode protected to the power rails. The measured values are stored in the Reading registers and compared with the Limit registers. The status bits in the Interrupt Status Register 1 and 2 are set if the measured values violate the programmed limits.

The Vccp voltage input measures the processor voltage, which will lie in the range of 0V to 3.0V.

The following table shows the values of the analog inputs that correspond to the min and max output codes of the A/D converter. For a complete list of the ADC conversions see Appendix A, "ADC Voltage Conversion," on page 83.

| INPUT VOLTAGE                                 | +12VIN  | +5VIN  | Vcc/3.3VIN | +2.5VIN | +1.8VIN | +1.5VIN | +Vccp  |

|-----------------------------------------------|---------|--------|------------|---------|---------|---------|--------|

| Min Value (Corresponds to A/D output 0000000) | <0.062  | <0.026 | <0.017     | <0.013  | <0.009  | <0.008  | <0.012 |

| Max Value (Corresponds to A/D output 1111111) | >15.938 | >6.640 | >4.383     | >3.320  | >2.391  | >1.992  | >2.988 |

#### Table 5.5 Min/Max ADC Conversion Table

## 5.8 Voltage ID

VID0-VID4 digital inputs are used to store processor Voltage ID codes (for processor operating voltage) in the VID0-4 register (43h). These VIDs can be read out by the management system using the SMBus interface.

## 5.9 Temperature Measurement

Temperatures are measured internally by bandgap temperature sensor and externally using two sets of diode sensor pins (for measuring two external temperatures). See subsections below.

**Note:** The temperature sensing circuitry for the two remote diode sensors is calibrated for a 3904 type diode.

## 5.9.1 Internal Temperature Measurement

Internal temperature can be measured by bandgap temperature sensor. The measurement is converted into digital format by internal ADC. This data is converted in two's complement format since both negative and positive temperature can be measured. This value is stored in Internal Temperature Reading register (26h) and compared to the Temperature Limit registers (50h - 51h). If this value violates the programmed limits in the Internal High Temperature Limit register (51h) or the Internal Low Temperature Limit register (50h) the corresponding status bit in Interrupt Status Register 1 is set.

If auto fan option is selected, the hardware will adjust the operation of the fans accordingly. See the section titled Auto Fan Control Operating Mode on page 30.

## 5.9.2 External Temperature Measurement

The Hardware Monitor Block also provides a way to measure two external temperatures using diode sensor pins (Remote x+ and Remote x-). The value is stored in the register (25h) for Remote1+ and Remote1- pins. The value is stored in the Remote Temperature Reading register (27h) for Remote2+ and Remote2- pins. If these values violate the programmed limits in the associated limit registers, then the corresponding Remote Diode 1 (D1) or Remote Diode 2 (D2) status bits will be set in the Interrupt Status Register 1.

If auto fan option is selected, the hardware will adjust the operation of the fans accordingly. See Auto Fan Control Operating Mode on page 30.

There are Remote Diode (1 or 2) Fault status bits in Interrupt Status Register 2 (42h), which, when one, indicate a short or open-circuit on remote thermal diode inputs (Remote x+ and Remote x-). Before a remote diode conversion is updated, the status of the remote diode is checked. In the case of a short or open-circuit on the remote thermal diode inputs, the value in the corresponding reading register will be forced to 80h. Note that this will cause the associated remote diode limit exceeded status bit to be set (i.e. Remote Diode x Limit Error bits (D1 and D2) are located in the Interrupt Status 1 Register at register address 41h).

The temperature change is computed by measuring the change in Vbe at two different operating points of the diode to which the Remote x+ and Remote x- pins are connected. But accuracy of the measurement also depends on non-ideality factor of the process the diode is manufactured on.

## 5.9.3 Temperature Data Format

Temperature data can be read from the three temperature registers:

- Internal Temp Reading register (26h)

- Remote Diode 1 Temp Reading register (25h)

- Remote Diode 2 Temp Reading register (27h)

The following table shows several examples of the format of the temperature digital data, represented by an 8-bit, two's complement word with an LSB equal to 1.0  $^{0}$ C.

| TEMPERATURE         | READING (DEC) | READING (HEX) | DIGITAL OUTPUT |

|---------------------|---------------|---------------|----------------|

| -127 <sup>0</sup> C | -127          | 81h           | 1000 0001      |

| ÷                   | ÷             | ÷             | ÷              |

| -50 <sup>0</sup> C  | -50           | CEh           | 1100 1110      |

| ÷                   | ÷             | ÷             | ÷              |

| -25 <sup>0</sup> C  | -25           | E7h           | 1110 0111      |

| ÷                   | ÷             | ÷             | ÷              |

| -1 <sup>0</sup> C   | -1            | FFh           | 1111 1111      |

| 0 <sup>0</sup> C    | 0             | 00h           | 0000 0000      |

| +1 <sup>0</sup> C   | 1             | 01h           | 0000 0001      |

| ÷                   |               | ÷             | ÷              |

| +25 <sup>0</sup> C  | 25            | 19h           | 0001 1001      |

| ÷                   |               | ÷             | ÷              |

| +50 <sup>0</sup> C  | 50            | 32h           | 0011 0010      |

| ÷                   | ÷             | ÷             | ÷              |

| +127 <sup>0</sup> C | 127           | 7Fh           | 0111 1111      |

| SENSOR ERROR        | 128           | 80h           | 1000 0000      |

## Table 5.6 Temperature Data Format

Fan Control Device with Hardware Monitoring and Acoustic Noise Reduction Features

#### Datasheet

## 5.9.4 Offset Registers

There are three offset registers:

- Offset Register Ambient (1Dh)

- Offset Register 2 (1Eh)

- Offset Register 1 (1Fh)

Offset Register 1 is used for Remote Diode 1 Temp Reading. Offset Register 2 is used for Remote Diode 2 Temp Reading. Offset Register Ambient is used for internal Temp Reading.

The Offset Registers contain a 2's complement value which is added (or subtracted if the number is negative) to the corresponding temperature reading. The default value in the offset register is zero, so initially zero is always added to the temperature reading.

## 5.10 Thermal Zones

Each temperature measurement input is assigned to a Thermal Zone to control the PWM outputs in Auto Fan Control mode. These zone assignments are as follows:

- Zone 1 = Remote Diode 1 (Processor)

- Zone 2 = Ambient (Internal) Temperature Sensor

- Zone 3 = Remote Diode 2

## Chapter 6 Fan Control

The following sections describe the various fan control and monitoring modes in the part.

## 6.1 General Description

This Fan Control device is capable of driving multiple DC fans via three PWM outputs and monitoring up to four fans equipped with tachometer outputs in either Manual Fan Control mode or in Auto Fan Control mode. The three fan control outputs (PWMx pins) are controlled by a Pulse Width Modulation (PWM) scheme. The four pins dedicated to monitoring the operation of each fan are the TACH[1:4] pins. Fans equipped with Fan Tachometer outputs may be connected to these pins to monitor the speed of the fan.

## 6.1.1 Limit and Configuration Registers

At power up, all the registers are reset to their default values and PWM[1:3] are set to "Fan always on Full" mode. Before initiating the monitoring cycle for either manual or auto mode, the values in the limit and configuration registers should be set.

The limit and configuration registers are:

- Registers 54h 5Bh: TACHx Minimum

- Registers 5Fh 61h: Zone x Range/FANx Frequency

- Registers 5Ch 5Eh: PWMx Configuration

- Registers 62h 63h: Min/Off, PWM x Ramp Rate Control

- Registers 64h 66h: PWMx Minimum Duty Cycle

- Registers 67h 69h: Zone x Low Temp LIMIT

- Registers 6Ah 6Ch: Zone x Temp Absolute Limit all fans in Auto Mode are set to full

- Registers 6Dh 6Eh: Zone x Hysteresis

- Register 81h: TACH\_PWM Association

- Registers 90h 93h: Tachx Option Registers

- Registers 94h 96h: PWMx Option Registers

The limit and configuration registers are defined in Chapter 7, Register Set.

#### Notes:

- The START bit in Register 40h Ready/Lock/Start Register must be set to '1' to start temperature monitoring functions.

- Setting the PWM Configuration register to Auto Mode will not take effect until after the START bit is set

## 6.1.2 Device Set-Up

BIOS will follow the steps listed below to configure the fan registers on this device. The registers corresponding to each function are listed. All steps may not be necessary if default values are acceptable. Regardless of all changes made by the BIOS to the limit and parameter registers during configuration, the EMC6D102 will continue to operate based on default values until the Start bit, in the Ready/Lock/Start register, is set. Once the Start bit is set, the EMC6D102 will operate according to the values that were set by BIOS in the limit and parameter registers.

- 1. Set limits and parameters (not necessarily in this order)

- a. [5F-61h] Set PWM frequencies and Auto Fan Control Range.

- b. [62-63h] Set Ramp Rate Control and min/off

- c. [5C-5Eh] Set the fan spin-up delays.

- d. [5C-5Eh] Match each PWM output with a corresponding thermal zone.

- e. [67-69h] Set the zone temperature low limits.

- f. [6A-6Ch] Set the zone temperature absolute limits.

- g. [64-66h] Set the PWM minimum duty cycle.

- h. [6D-6Eh] Set the zone temperature Hysteresis values.

- i. [81h] Associate a Tachometer input to a PWM output Register

- j. [90-93h] Select the TACH Mode of operation (Mode 1 or Mode 2)

- k. [90-93h] Programmed the PWM Max Stretch time (Mode 2 only)

- I. [90-93h] Set the number of edges per tach reading

- m. [90-93h] Set the ignore first 3 edges of tach input bit

- n. [90-93h] Set the SLOW bit if tach reading should indicated slow fan or stalled fan event as FFFFh.

- o. [94-96h] Set the TACH Reading Update rate

- p. [94-96h] Set the tach reading guard time (Mode 2 Only)

- q. [94-96h] Set the TACH reading logic for Opportunistic Mode (Mode 2 Only)

- r. [94-96h] Set the SZEN bit, which determines if the PWM output will ramp to Off or jump to Off.

- 2. [40h] Set bit 0 (Start) to start monitoring.

- 3. [40h] Set bit 1 (Lock) to lock the limit and parameter registers (optional)

## 6.1.3 PWM Fan Speed Control

Note: The following description applies to PWM1, PWM2, and PWM3.

When describing the operation of the PWMs, the terms "Full on" and "100% duty cycle" means that the PWM output will be high for 255 clocks and low for 1 clock (INVERT bit = 0). The exception to this is during fan spin-up when the PWM pin will be forced high for the duration of the spin-up time.

## 6.1.3.1 Manual Fan Control Operating Mode (Test Mode)

When operating in Manual Fan Control Operating Mode, software controls the speed of the fans by directly programming the PWM duty cycle. The operation of the fans can be monitored based on reading the temperature and tachometer reading registers and/or by polling the interrupt status registers. The EMC6D102 offers the option of generating an interrupt indicated by the INT# signal located on the PWM2 and TACH3 pins.

To control the PWM outputs in manual mode:

- Write '111' to bits[7:5] Zone/Mode, located in Registers 5Ch-5Eh: PWMx Configuration.

- The speed of the fan is controlled by the duty cycle set for that PWM output. The duty cycle must be programmed in Registers 30h-32h: Current PWM Duty

To monitor the fans:

Fans equipped with Tachometer outputs can be monitored via the TACHx input pins. See Section 6.1.4, "Fan Speed Monitoring," on page 37.

If an out-of-limit condition occurs, the corresponding status bit will be set in the Interrupt Status registers. Setting this status bit will generate an interrupt signal on the INT# pin (if enabled). Software must handle the interrupt condition and modify the operation of the device accordingly. Software can evaluate the operation of the Fan Control device through the Temperature and Fan Tachometer Reading registers.

When in manual mode, the current PWM duty cycle registers can be written to adjust the speed of the fans, when the start bit is set. These registers are not writable when the lock bit is set.

**Note:** The PWMx Current Duty Cycle register is implemented as two separate registers: a read-only and a write-only. When a value is written to this register in manual mode there will be a delay before the programmed value can be read back by software. The hardware updates the read-only PWMx Current Duty Cycle register on the beginning of a PWM cycle. If Ramp Rate Control is disabled, the delay to read back the programmed value will be from 0 seconds to 1/(PWM frequency) seconds. Typically, the delay will be 1/(2\*PWM frequency) seconds.

## 6.1.3.2 Auto Fan Control Operating Mode

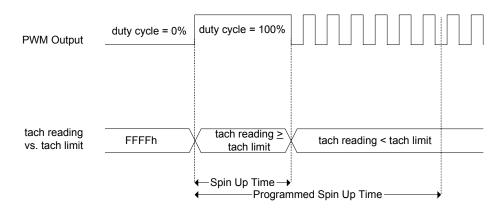

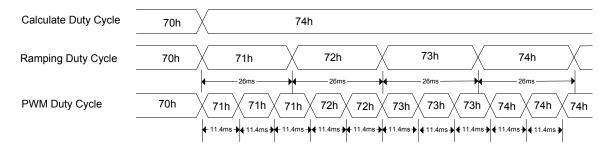

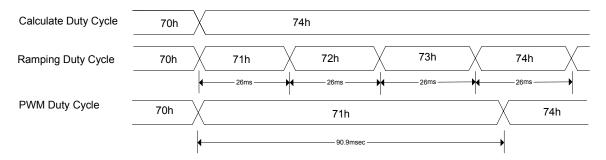

The EMC6D102 implements automatic fan control. In Auto Fan Mode, this device automatically adjusts the PWM duty cycle of the PWM outputs, according to the flow chart on the following page (see Figure 6.1 Automatic Fan Control Flow Diagramon page 31).