# QorlQ P5020/P5010 Processors

#### **Overview**

The QorlQ P5 family delivers scalable 64-bit processing with single-, dual- and quad-core devices. With frequencies scaling up to 2.0 GHz, a tightly coupled cache hierarchy for low latency and integrated hardware acceleration, the P5020 (dual-core) and P5010 (single-core) devices are ideally suited for compute intensive, power-conscious control plane applications.

## QorlQ P5020/P5010 Processors

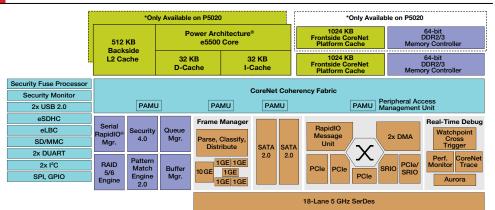

Core Complex (CPU, L2 and Frontside CoreNet Platform Cache)

Accelerators and Memory Control Networking Elements

## P5 Family Comparison Chart

|                    | P5020/P5010                        | P5040/P5021                      |

|--------------------|------------------------------------|----------------------------------|

|                    |                                    |                                  |

| CPU cores          | 2x 64-bit e5500, 1x (P5010)        | 4x 64-bit e5500, 2x (P5021)      |

| Threads            | 2/1 (single thread per core)       | 4/2 (single thread per core)     |

| Max core frequency | 1.6 to 2.0 GHz                     | 1.8 to 2.4 GHz                   |

| L2                 | 512 KB per core                    | 512 KB per core                  |

| L3/Platform        | 2 MB (P5020)/1 MB (P5010)          | 2 MB (both P5040 and P5021)      |

| DDR I/F            | 2x 64-bit DDR3 (up to 1333 MT/s)   | 2x 64-bit DDR3 (up to 1600 MT/s) |

|                    | 1x 64-bit DDR3 (P5010)             |                                  |

| PCI Express®       | 4x PCle v2.0                       | 3x PCIe v2.0 (incl. 1 x 8)       |

| GbE, 10 GbE        | 5x 1 GbE, 1x 10 GbE                | 10x 1 GbE, 2x 10 GbE             |

| SRIO               | 2x SRIO v2.1                       | N/A                              |

|                    | (supports Type 9 and 11 messaging) |                                  |

| SerDes lanes       | 18 lanes                           | 20 lanes                         |

| Package            | 1295-pin 37.5 x 37.5 mm FC-PBGA    | 1295-pin 37.5 x 37.5 mm FC-PBGA  |

#### e5500 Core

The P5020 is based on the 64-bit e5500 Power Architecture® core. The e5500 core uses a seven-stage pipeline for low latency response to unpredictable code execution paths, boosting its single-threaded performance. Key features:

- Supports up to 2.0 GHz core frequencies

- Tightly-coupled low latency cache hierarchy: 32 KB I/D (L1), 512 KB L2 per core

- Up to 2 MB of shared platform cache (L3)

- 3.0 DMIPS/MHz per core

- Up to 64 GB of addressable memory space

- Hybrid 32-bit mode to support legacy software and seamless transition to 64-bit architecture

#### Virtualization

The P5020 includes support for hardwareassisted virtualization. The e5500 core offers an extra core privilege level (hypervisor). Virtualization software for the P5 family includes kernel-based virtual machine (KVM), Linux<sup>®</sup> containers, Freescale hypervisor and commercial virtualization software from Green Hills<sup>®</sup> Software and Enea<sup>®</sup>.

#### Target Markets and Applications

The P5020 is designed for highperformance, power-constrained control plane applications and provides an ideal combination of core performance, integrated accelerators and advanced I/O required for the following compute-intensive applications:

- Enterprise equipment: Router, switch, services

- Data center: Server appliance, SAN storage controller, iSCSI controller, FCoE bridging

- Aerospace and defense

- Industrial computing: Single-board computers, test/measurement, robotics

## DPAA Hardware Accelerators

| Frame manager (FMAN)             | 12 Gb/s classify, parse<br>and distribute                                                           |

|----------------------------------|-----------------------------------------------------------------------------------------------------|

| Buffer manager (BMAN)            | 64 buffer pools                                                                                     |

| Queue manager (QMAN)             | Up to 2 <sup>24</sup> queues                                                                        |

| Security (SEC)                   | 17 Gb/s: 3 DES, AES                                                                                 |

| Pattern matching engine<br>(PME) | 10 Gb/s aggregate                                                                                   |

| RapidIO <sup>®</sup> manager     | Supports type 9 and type 11 messaging                                                               |

| RAID5/6 engine                   | Calculates parity for<br>network attached<br>storage and direct<br>attached storage<br>applications |

## Data Path Acceleration Architecture (DPAA)

The P5020 integrates QorlQ DPAA, an innovative multicore infrastructure for scheduling work to cores (physical and virtual), hardware accelerators and network interfaces. The FMAN, a primary element of the DPAA, parses headers from incoming packets and classifies and selects data buffers with optional policing and congestion management. The FMAN passes its work to the QMAN, which assigns it to cores or accelerators with a multilevel scheduling hierarchy. The P5020 also offers accelerators for cryptography, enhanced regular expression pattern matching and RAID5/6 offload.

#### System Peripherals and Networking

For networking, the FMAN supports one 10 Gb/s and 5x 1 Gb/s MAC controllers that connect to PHYs, switches and backplanes over RGMII, SGMII and XAUI. High-speed system expansion is supported through four PCI Express® v2.0 controllers that support a variety of lane widths. Other peripherals include SATA, SD/MMC, I<sup>2</sup>C, UART, SPI, NOR/NAND controller, GPIO and dual 1333 MT/s DDR3/3L controllers.

## P5020/P5010 Features List

| Two (P5020) or one (P5010)<br>single threaded e5500 cores<br>built on Power Architecture®<br>technology | <ul> <li>Up to 2.0 GHz with 64-bit ISA support (Power Architecture V2.06 compliant)</li> <li>Three levels of instruction: User, supervisor, hypervisor</li> <li>Hybrid 32-bit mode to support legacy software and transition to 64-bit architecture</li> </ul>                                                                                            |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CoreNet platform cache (CPC)                                                                            | 2.0 MB configured as dual 1 MB blocks (1 MB only for P5010)                                                                                                                                                                                                                                                                                               |

| Hierarchical interconnect fabric                                                                        | <ul> <li>CoreNet fabric supporting coherent and non-coherent transactions with<br/>prioritization and bandwidth allocation amongst CoreNet endpoints</li> <li>QMAN fabric supporting packet-level queue management and quality of<br/>service scheduling</li> </ul>                                                                                       |

| Two 64-bit DDR3/3L SDRAM<br>memory controllers with ECC<br>and interleaving support                     | <ul><li>Up to 1333 MT/s</li><li>Memory pre-fetch engine</li></ul>                                                                                                                                                                                                                                                                                         |

| DPAA incorporating acceleration for the following functions                                             | <ul> <li>Packet parsing, classification and distribution (FMAN)</li> <li>QMAN for scheduling, packet sequencing and congestion management</li> <li>Hardware BMAN for buffer allocation and de-allocation</li> <li>Cryptography acceleration (SEC 4.2) at up to 40 Gb/s</li> <li>RegEx pattern matching acceleration (PME 2.1) at up to 10 Gb/s</li> </ul> |

| SerDes                                                                                                  | <ul><li>18 lanes at up to 5 Gb/s</li><li>Supports SGMII, XAUI, PCIe rev1.1/2.0, SATA</li></ul>                                                                                                                                                                                                                                                            |

| Ethernet interfaces                                                                                     | <ul><li>One 10 Gb/s Ethernet MACs</li><li>5x 1 Gb/s Ethernet MACs</li></ul>                                                                                                                                                                                                                                                                               |

| High-speed peripheral interfaces                                                                        | <ul> <li>Four PCI Express 2.0 controllers</li> <li>Two Serial RapidIO<sup>®</sup> controllers/ports (sRIO port) v1.3-compliant with features of v2.1</li> <li>Two serial ATA (SATA 2.0) controllers</li> </ul>                                                                                                                                            |

| Additional peripheral interfaces                                                                        | <ul> <li>Two Full-Speed USB 2.0 controllers with integrated PHY</li> <li>Enhanced secure digital host controller (SD/MMC/eMMC)</li> <li>Enhanced serial peripheral interface</li> <li>Four I<sup>2</sup>C controllers</li> <li>Four UARTs</li> <li>Integrated flash controller supporting NAND and NOR flash</li> </ul>                                   |

| DMA                                                                                                     | Dual four channel                                                                                                                                                                                                                                                                                                                                         |

| Support for hardware<br>virtualization and partitioning<br>enforcement                                  | Extra privileged level for hypervisor support                                                                                                                                                                                                                                                                                                             |

|                                                                                                         | Secure boot, secure debug, tamper detection, volatile key storage                                                                                                                                                                                                                                                                                         |

#### Software and Tool Support

- Enea: Real-time operating system support and virtualization software

- Green Hills: Comprehensive portfolio of software and hardware development tools, trace tools, real-time operating systems and virtualization software

- Mentor Graphics<sup>®</sup>: Commercial-grade Linux solution

- QNX<sup>®</sup>: Real-time OS and development tool support

- QorlQ P5020 development system (P5020DS-PB)

### For more information, please visit freescale.com/QorlQ

Freescale, the Freescale logo and QorlQ are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm Off. CoreNet is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. © 2012, 2013 Freescale Semiconductor,Inc.

**Freescale**

Document Number: QP5020FS REV 4